I am posting again because of an error in post. Forgive me if my post is a multi post.

Hi all,

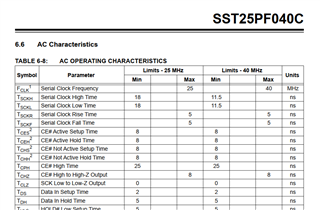

The external SPI Flash memory I use has a maximum clock rise time(SCKR) fall timeTSCKF) of 5ns.

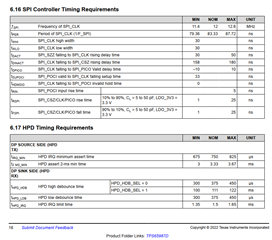

The TPS65987D requirement is 1~25ns(tRSPI, tFSPI), but the CLK is output by the TPS65987D, so I thought it would not satisfy the SPI Flash memory specification.

However, the memory vendor said that the TPS65987D specification is a requirement, so it works with the memory specification. Does TI tolerate this memory usage?

Incidentally, the actual measurement in my system was tRSPI=13ns, tFSPI=11.6ns at room temperature.

Best Regards,

Yukio Oyama