Other Parts Discussed in Thread: CSD17304Q3, TPS51116

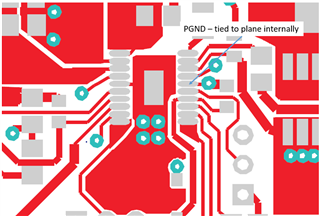

I am using the TPS51116 in DCAP mode for a 1.35V output. I am using Rds_on sensing, with a high/low-side TI CSD17304Q3 FET.

I am seeing unusual behavior of the part at around 1.8A output. Below 1.8A the part operates normally. When I first observed this behavior, I increased my RTRIP resistor thinking the part was in OC limit, but even after I increased the resistor to increase the OC limit, the part still shutdown at 1.8A again.

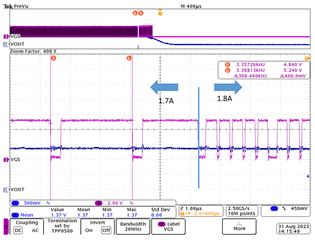

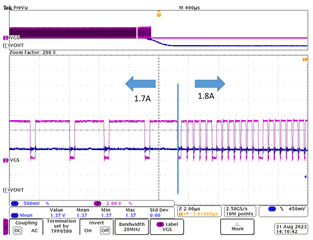

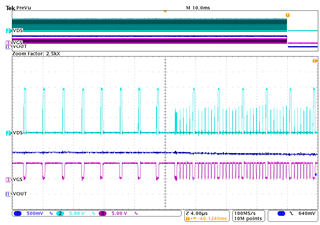

The scope capture below (Vgs low-side FET in pink, Vout in blue) shows the part operating normally at around 400kHz switch frequency below 1.8A. When the load current is beyond 1.8A, the switch frequency increases to about 2.2MHz. I didn't think the part would go into a 2.2MHz operation, with the normal frequency set around 400kHz.

I also captured the LL pin (i.e. switch node in teal) since this doubles as the current-sense point when using Rds_on sensing. The switch node appears to be oscillating which lines up with the time that the Vgs increases in frequency. I have a snubber R and C on the switch node if there is some sort of oscillation occuring, but I do not see how going to a higher output current would cause this oscillation when at lower load currents the oscillation would occur.

Does the DCAP mode need to sense the inductor current mode when using Rds_on sensing? I am wondering if I should change my low-side FET to a part with higher Rds_on to get more signal for sensing the inductor current. I am not sure why the output would work a lower currents with less signal and then start shutting down at higher currents when there is more signal at the LL pin, but it was just an idea if the output is going unstable.

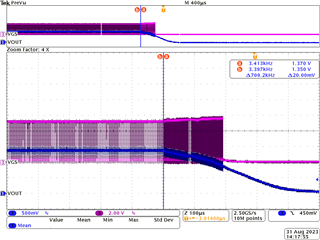

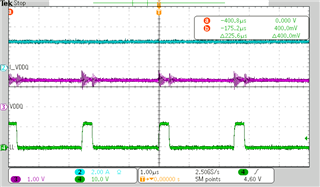

The final scope capture shows the 1.35V output slowly dropping to zero when I step the load to 1.8A.

Has anyone seen this behavior before?