Note: the component designations that I am referring to in this post come from the data sheet of the UCC27223

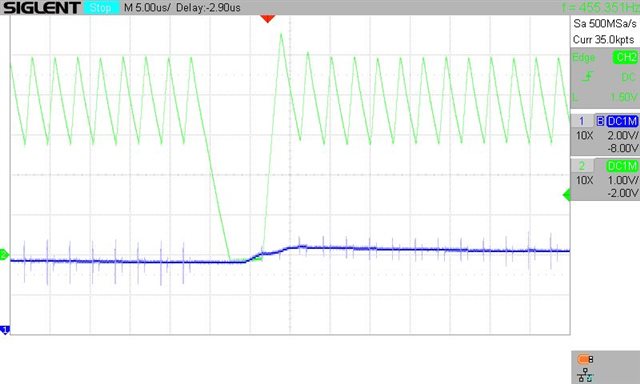

I am monitoring the VLO voltage (on C2) under changing load and input voltage conditions. What I am finding is that under high output load and high input voltage, the VLO voltage drops below 3.9V, which is triggering an UVLO condition. I have confirmed that the input voltage to pin 3 (VDD) is not dropping too low, and I have put 3x 10uF ceramic caps in parallel right next to the UCC27223 so that the input voltage stays steady under load.

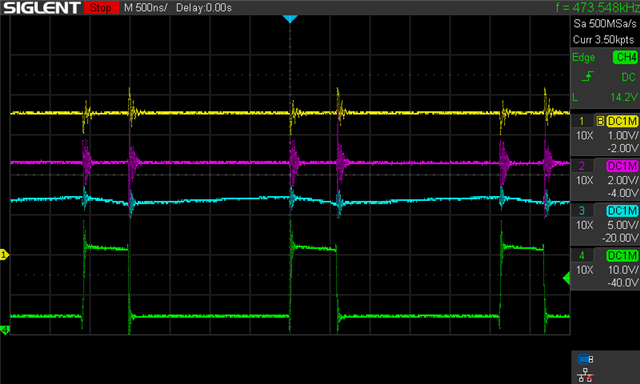

I think there is something that I do not understand about the generation of VLO inside the IC. Here is an image of what is happening:

Ch1 (blue) VLO signal.

Ch2 (green): output current waveform, around 4A RMS in this example

- VLO has a slow decay, and when it drops to around 3.9V, the UCC resets. When there is no load, VLO pops back up to around 4.2V and the UCC restarts.

I have experimented with different current ratings of the Schottky diode D1 (1A vs 3A). This does not have any effect.

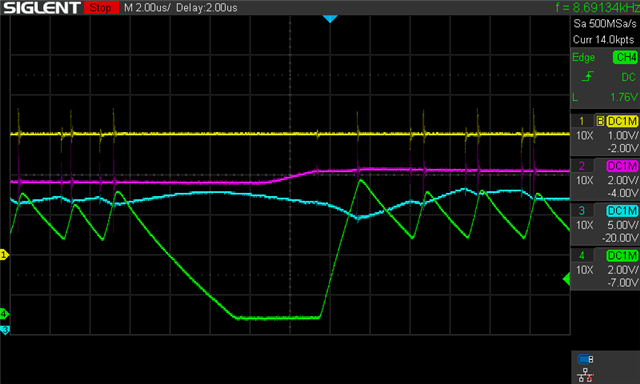

I have changed the value of the VHI resistor R1. 0 Ohms is the worst - the reset occurs at around 4A RMS output as shown in the image above. When R1 is changed to 4.7 Ohms, the output current can be increased to around 6A RMS before the UVLO reset occurs. Increasing R1 to 10 Ohms does not offer any improvement over 4.7 Ohms. For reference I have included a table below showing the various FET's that I am experimenting with. All have fairly low/fairly similar gate charge specifications.

Reducing the value of C2 from 2x1uF MLCC to a single 100nF capacitor definitely makes the problem worse: in this condition the ULVO triggers at around 2A RMS output.

I have experimented with different values of C1, from 100nF to 220nF but this shows minimal improvement.

What I find curious is that at a given output current level, say 5A RMS for example, if I increase the input voltage from 14V to 17V in 1V increments, the UVLO reset gets worse. At 17Vin, the load has to be dropped to 3A RMS to keep the UVLO from triggering. If I reduce the input voltage to 12V, then I can increase the output current to 6A RMS and UVLO does not trigger. When I bump it up to 7A then UVLO will start to trigger.

The UCC27223 data sheet says that C2 should not be more than 4.7uF. At this point I need some guidance as I think that the issue may be a combination of values for C2, C1, R1, and D1 for the target FET's that I am using.

For reference:

Vin: 10-17V

PWM input is coming from a hysteresis-drive circuit (output is a current source). I am sensing the output current with a INA180A2 fed into a high-speed op-amp to create the PWM Input signal for pin 7. I can share the schematic if you send a private link to me.

The operating frequency is around 300-350kHz. The frequency varies with load and Vin. I would like to move to a higher frequency if there is an improvement in efficiency.

Thoughts?