Other Parts Discussed in Thread: HD3SS6126,

Hi Team

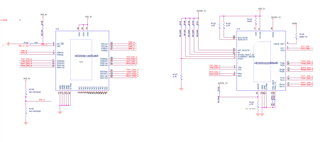

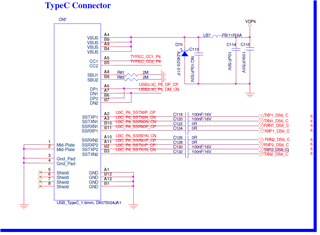

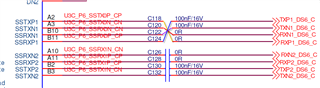

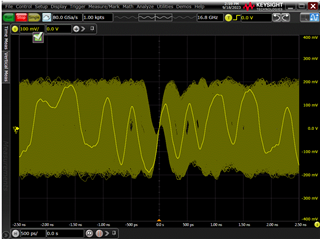

I've designed the HD3SS3220 USB3.0 port controller to as a USB 3.0 SuperSpeed 2:1 MUX in the PCB board. After power on the PCB board but the SuperSpeed MUX it doesn't work normally. To observe the waveform but there's no LFPS signal can be measured. So the system of HD3SS3220 + HD3SS6126 can't implement to SuperSpeed USB3.0 transfer data rate, it's only support USB2.0 transfer data rate.

Can you help to have some suggestion.

Schematic: