I'd like to check if we still can use DTX-3.3 LDO solution with following condition

Vin=12V Vout=3.3V Iout=0.1605A ambient=50C.

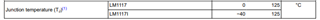

The power loss is around (12-3.3)*0.1605=1.4W. But I found the Power loss Figure 9-14 is almost on limitation.

Only Theta JA=47C can margin support.

So, I'd like to check if we still can we this solution. Any recommendation need?