Hi,

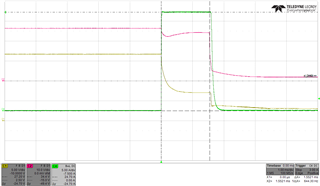

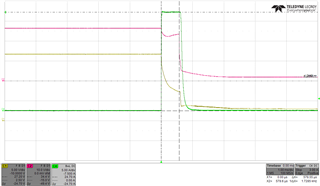

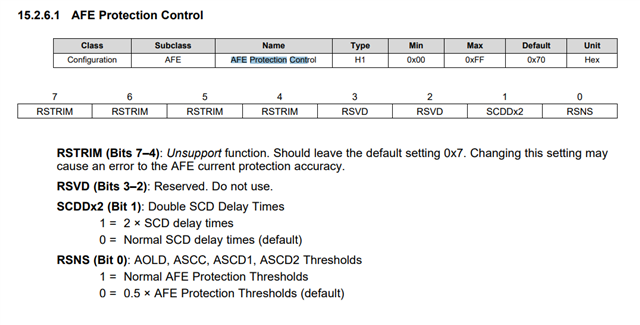

Customer is using the BQ40Z50 on a design and seeing a time delay of 300-400us for an overcurrent event and the activation of protection (CHG/DSG signal change at the BQ). They expected tDetect delay of 160us but they are seeing double that. They set the time offset for 0 seconds for protections.

Is this expected behavior? Any suggestions on how to reduce the time from event to protect?

Thanks,

Tyler