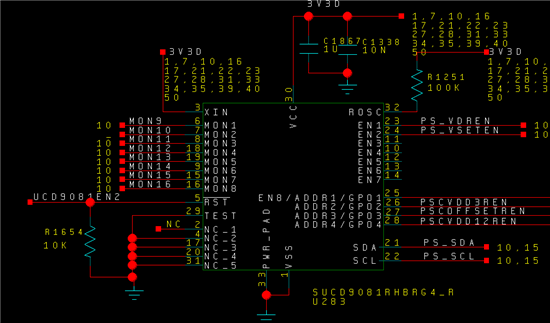

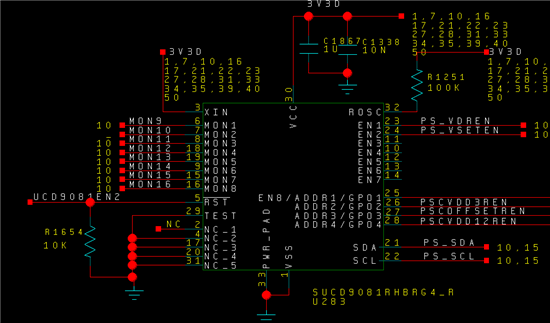

May I connect the reset pin of UCD9081 to FPGA as in attached figure?

How long time I can keep the reset pin of UCD9081 low?

Are there any potential issues?

Many Thanks.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

May I connect the reset pin of UCD9081 to FPGA as in attached figure?

How long time I can keep the reset pin of UCD9081 low?

Are there any potential issues?

Many Thanks.

For some reason, your original post did not come through. So, sorry for the delay. Pasting directly from a MS Word document may at times cause the forum post to come through "blank" with no original question. Either way, our IT fixed this post so I can see your original question.

UCD9081 RESET may be controlled with a separate device but usually the power supply sequencer powers up first, then enables the system power supplies (including any supply for an FPGA, etc.). When UCD9081 RESET is asserted, the EN and GPO pins become inputs and get configured after RESET is released. A simple R-C on UCD9081 RESET is usually sufficient. You can refer to the UCD9081 datasheet for more specifics on RESET pin timing.