Hi,

I'm using Pspice for TI + TPS62933 PSpice Transient Model to simulte the circuit. According to the example design, Vin=24V, Output=5V 3A. The buck IC operates at around 500kHz (2us period). In the PSpice simulation profile, if I increase "max step size" value, the simulation result will be incorrect after a certain max step size threshold.

run to time=200us for all trails

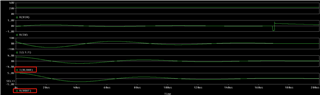

Trail 1: max step size=5ns

Trial 2: max step size=20ns

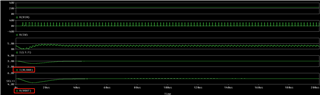

Trail 3: max step size=40ns

Trail 4: max step size=50ns