Hello,

We have issue with updating Current register during run time in case of applying this test (doing Software and Hardware reset more than one time).

Our current software implementation is sending the following frames (unlocking sequence) for one time during initialization:

1- Broadcast Write frame to CLR register with address <0x91> and data value <0x07>.

2- Broadcast Write frame to CTRLGATE register with address <0x96> and data value <0x43>.

3- Broadcast Write frame to CTRLGATE register with address <0x96> and data value <0x4F>.

4- Broadcast Write frame to CTRLGATE register with address <0x96> and data value <0x44>.

5- Broadcast Write frame to CTRLGATE register with address <0x96> and data value <0x45>.

6- Broadcast Write frame to LOCK register with address <0x93> and data value <0x00>.

7- Broadcast Write frame to EN0 register with address <0x90> and data value <0x77 , 0x77 , 0x77, 0x77>.

Before applying test we can update current register but after we can't.

Here it's our investigation:

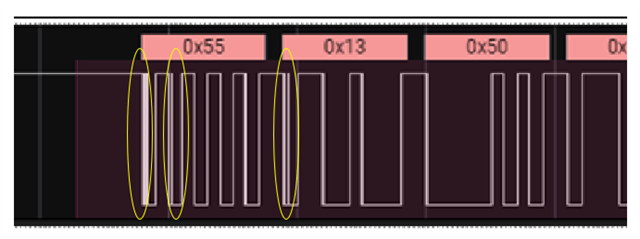

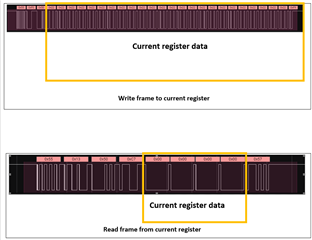

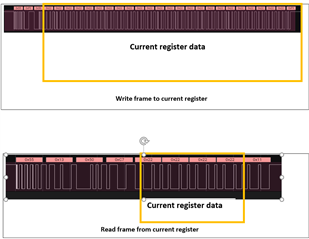

1- We tried to read Current register after updating it but as we see below current register not updated

2- We tried to send the each unlocking pervious frame with interframe delay (20ms) but the same issue.

3- We tried to send the unlocking frames periodically and issue is resolved and we managed to read current register as attached below

So please we need to know the best practice to send unlocking sequence to resolve the issue even if we apply the test because of sending them periodically, will impact bus load.