Other Parts Discussed in Thread: BQ24296M

Hi,

I have some questions and schematic review demand as below.

1.How long does it take for the Shipping mode to be entered after setting REG07[5] to 1 (BATFET_DISABLE) via I2C?

2.When the input current limit is set to 1A, PSEL is connected to GND, and OTG is left unconnected?

3.Can the QON pin be left unconnected when not using a physical button to exit Shipping mode?

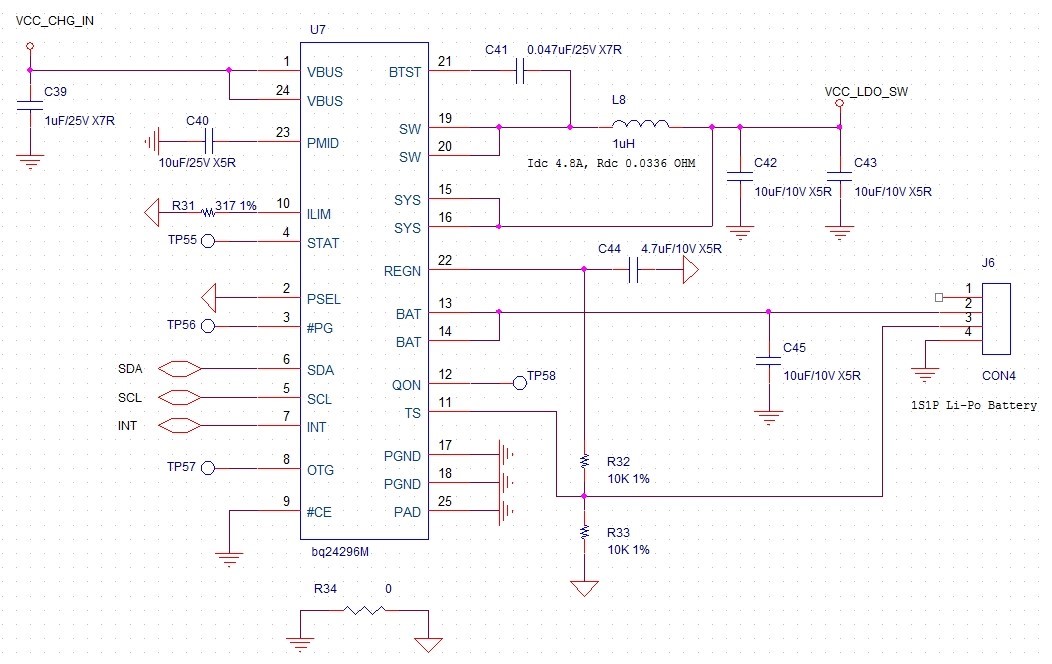

4.Please assist in verifying if the following circuit has any errors.