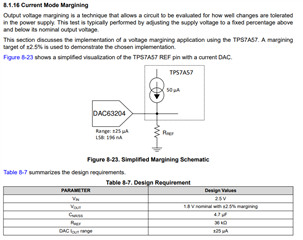

Other Parts Discussed in Thread: DAC63204

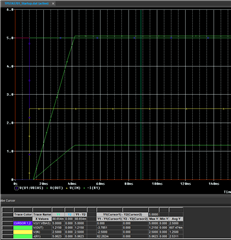

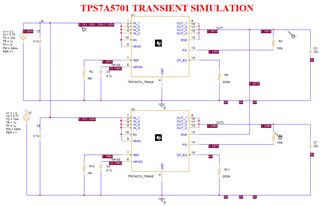

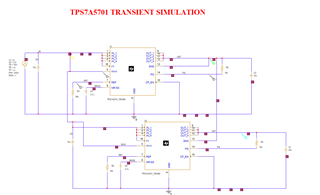

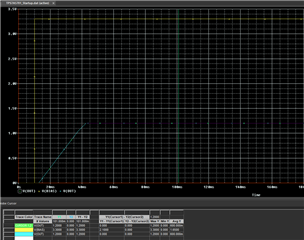

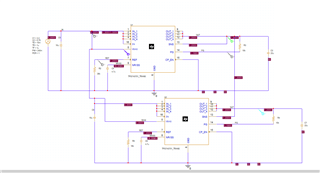

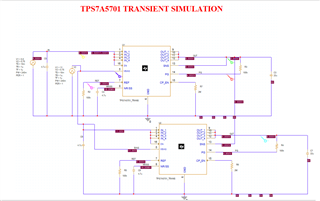

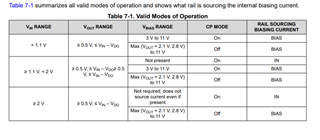

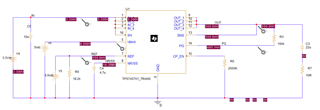

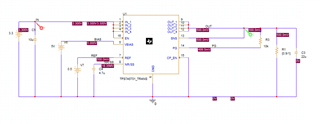

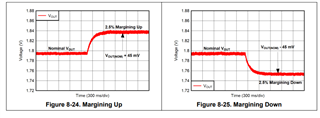

According to feedback resistor, we set the output voltage but in simulation (PSpice) we notice that if the output voltage exceeds the 1.2v, the simulation stuck and gives the error. It looks like the output move than 1.2V is not supported. Can you check and confirm why this is happening?

Mohsin