Hello,team

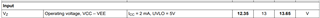

I would like to consult about LM5067, the customer's current application is like this, VCC=5V, VEE=-48V, these two signals are not powered on together, in the first stage VCC=5V, VEE=0V; In the second stage is VCC=5V, VEE=-48V, the current problem is that when VEE=0V, the Vout=5V=VCC of LM5067, but the maximum voltage of the customer's post-chip can not exceed 0.3V, so they now use a clamping diode to clamp VCC to 0.3V,so my question is

1、when VEE is enabled, the LM5067 output becomes VEE. Whether the chip is able to keep the output from following VCC.

2. When VCC=5V, VEE=0V, the chip is in the UVLO stage, why is the output of the chip equal to VCC, what is the specific path that causes it, it is found that the rise time of VOUT=VCC is only about 70ms.

3. Can the chip always work in the ULVO state?

4. Whether the clamping diode can be used for a long time