Hi.

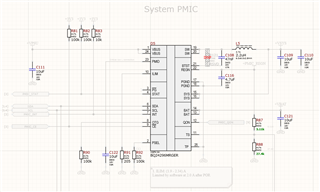

Our prototype design with BQ24296M has an EMI issue. Could you look at the design? Maybe there is something I'm missing.

Issue description:

- The design shows vast RF noise floor degradation (up to 10 dB @ 868 MHz) when supplied from the +VPSU.

- The noise floor degradation correlates with the applied +VSYS load (more current - more noise). There is no noise with a light load (<300 mA)

- The amount of noise doesn't change while replacing the +VPSU source.

- Replacing the inductor with a fully shielded one or adding the ferrite bead at +VPSU doesn't affect the noise.

- Replacing the VBUS decoupling capacitor with 1 uF makes the noise worse.

Additional information regarding this system:

- IINLIM 2.0 A

- VSYSMIN 3.5 V

- ICHG 640 mA

- Average system current w/o charging - 250-300 mA

- Peak system current w/o charging ~3.5 A (short GSM bursts)

- The 868 MHz transceiver has a 32 MHz crystal, so it may be sensitive to the noise harmonics on 64 MHz, 96 MHz, 128 MHz, etc.

The schematic:

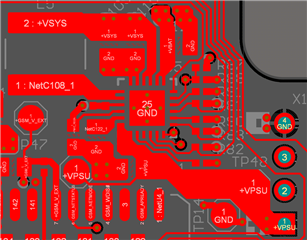

The layout (4L PCB, SIG+PWR - GND - GND+PWR - SIG+GND):