Other Parts Discussed in Thread: BQSTUDIO

The ALRT_PIN, DDSG_PIN, and DCHG_PIN bits in the FET Status register are asserted. However, no protection or PF trigger has been identified.

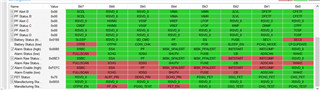

Meanwhile, the SSBC, SSA, and PF bits in the Alarm Status register are deasserted (please refer to the attached figure).

I've attached my data memory configuration, which was obtained from bqStudio.

I strongly suspect that the problem may be related to my incorrect configuration since the chip's default settings are functional.

Could someone provide guidance or advice for debugging? Thank you.