Other Parts Discussed in Thread: UCD90320

Hi,

Currently, we designed using a TPS543A26 part for multiple voltage rail power generations. In this Buck converter, Enable pin mentioned as current driven logic and also in datasheet mentioned "if going to provide the external digital control to enable pin, need to configure as an open drain/collector."

In our circuit, power monitoring & sequencing IC UCD90320 LGPO pin connected to enable of TPS543A26 with pull-down of 10K. By default, we are configuring LGPO pins as low driving and will be enabled by one-by-one power rails.

Our query is, whether it is mandatory to configure the enable pin as open drain in UCD90320?

It will impact any current driven issues? or pull down is suffient during OFF state?

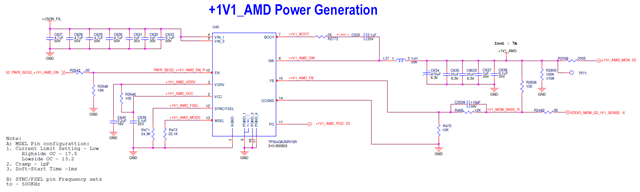

Also, Required your support to review the another Buck converter design. Please find the below DC-DC design for reference,

Thanks,

Dinesh