Other Parts Discussed in Thread: TPS62442-Q1, RM46L852, LM26420, LAUNCHXL2-RM46, PSPICE-FOR-TI

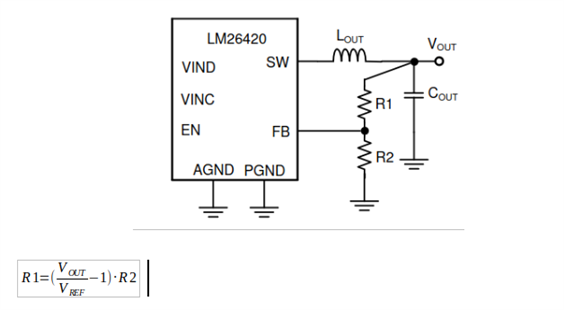

Hello, my name is Francisco, engineer of the R+D+i Department of Rother Industries & Technology company. I would like to verify the calculations made for my power circuit design using the LM26420Q1XMHX/NOPB DC/DC converter.

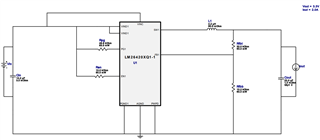

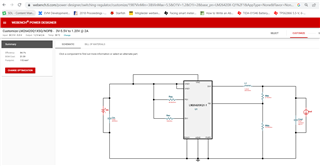

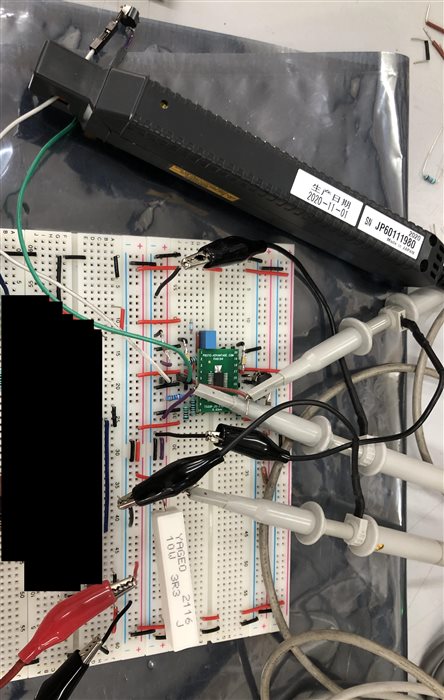

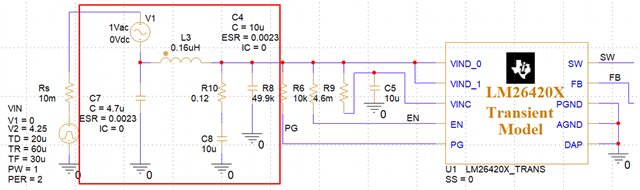

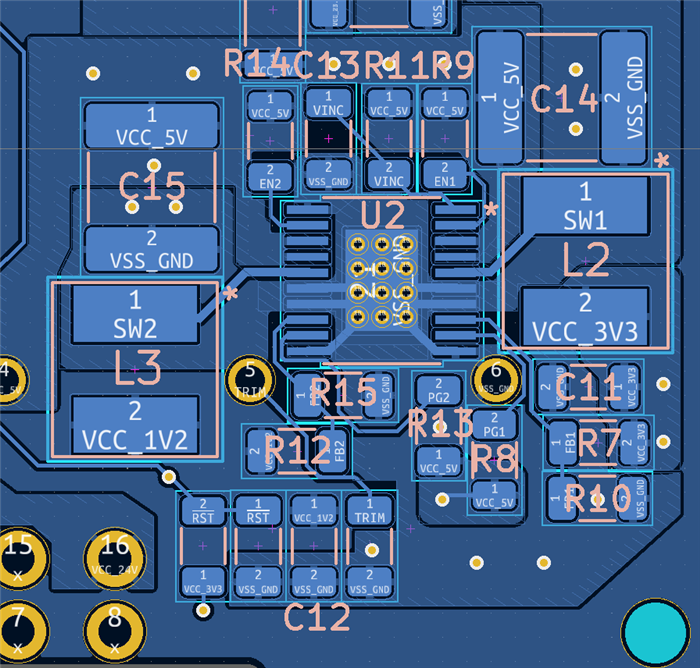

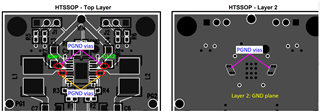

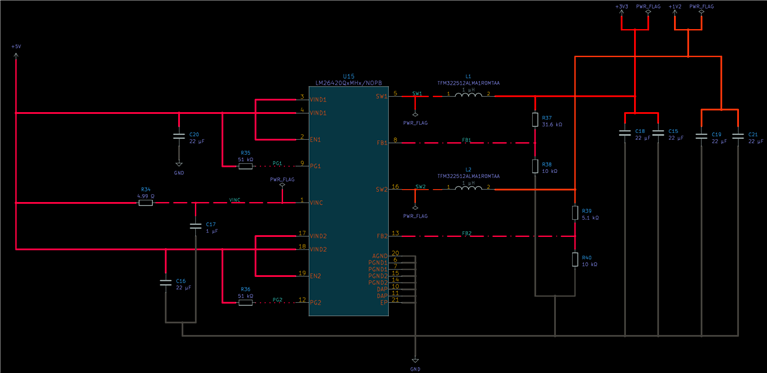

I attach the design of my power circuit.

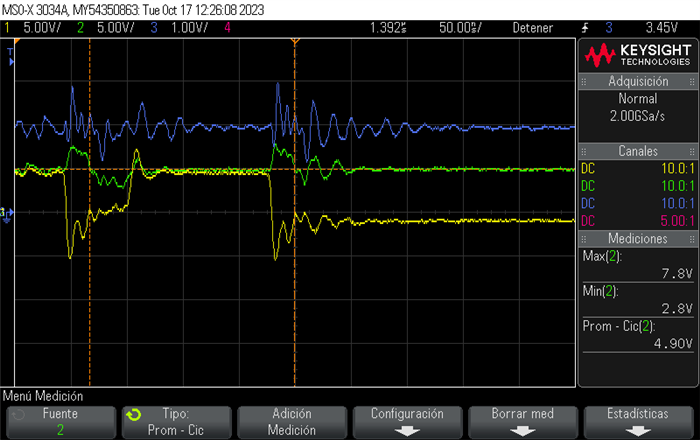

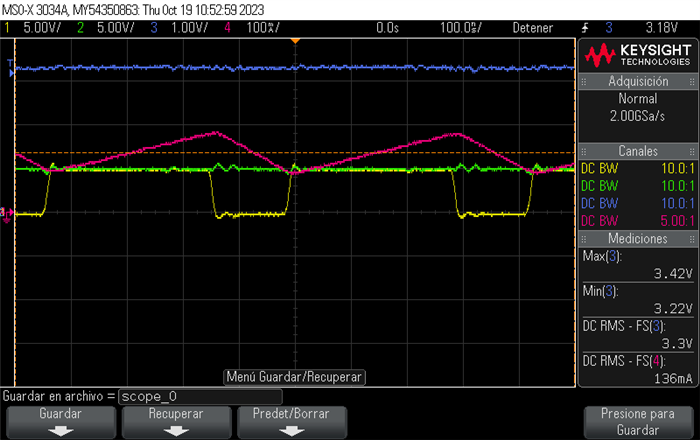

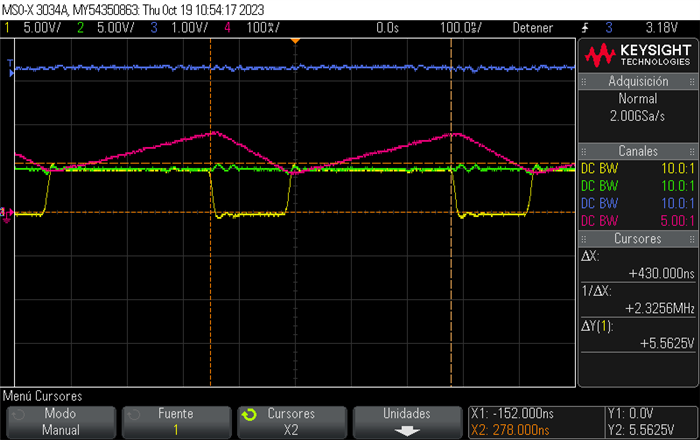

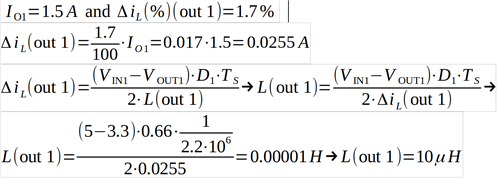

To obtain V_OUT=3.3 V and Iout (max)=2 A:

V_IN=5 V, F_s=2.2 MHz

V_REF=0.8 V and R2=10 kΩ

R1= 31.6 kΩ

I_LPK=2.4 A

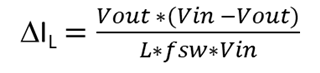

Δi_L=0.2

D=3.3/5

T_s=1/fs=1/2.2 MHz=454.54 ns

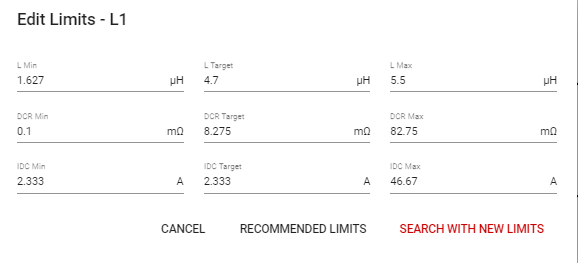

L=0.64 μH -> 1 μH

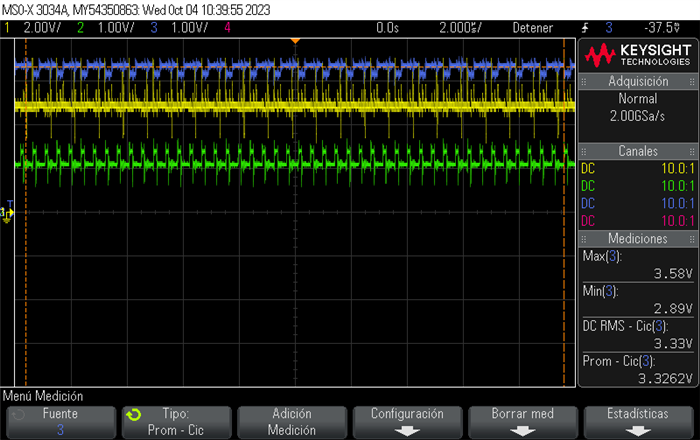

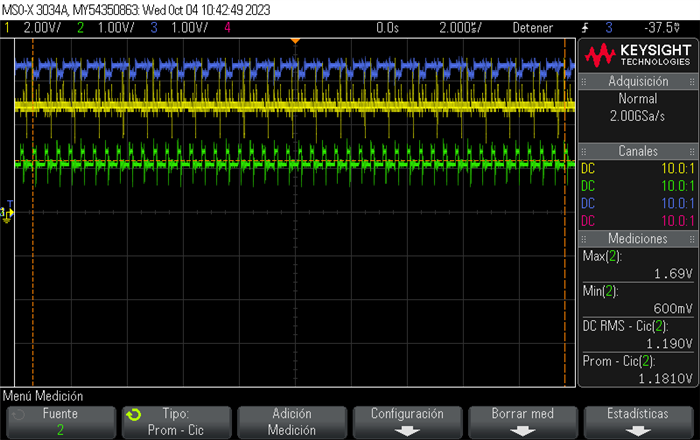

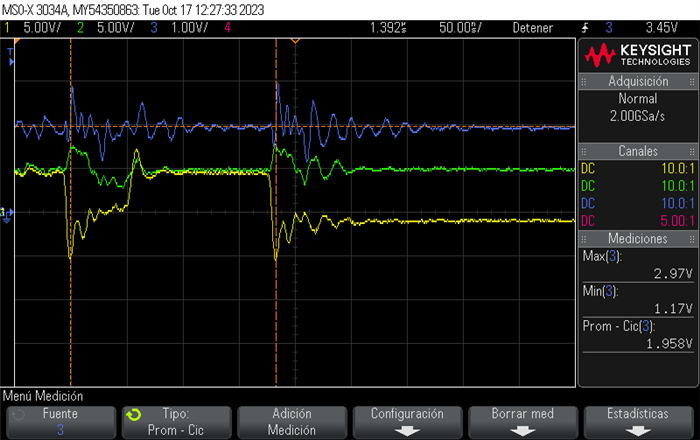

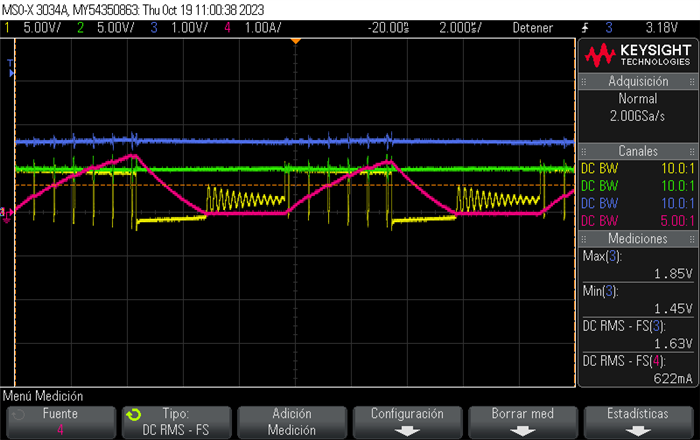

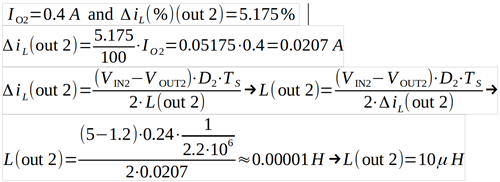

To obtain V_OUT=1.2 V and Iout (max)=2 A:

V_IN=5 V, F_s=2.2 MHz

V_REF=0.8 V and R2=10 kΩ -> R1= 5.1 kΩ

I_LPK=2.4 A

Δi_L=0.2

D=1.2/5

T_s=1/fs=1/2.2 MHz=454.54 ns

L=0.52 μH -> 1 μH

I use the following components:

The TFM322512ALMA1R0MTAA inductances of 1μH, the CL21A226KOQNNNG capacitor of 22 μF, the YR1B31K6C resistance of 31.6 kohm, the LR1F10K resistance of 10 kohm, the H85K11BC resistance of 5.1 kohm, the MBA02040C4998FC100 resistance of 4.99 ohm, the LR1F51K resistance of 51 kohm and the B32529C0105J189 capacitor of 1 μF.

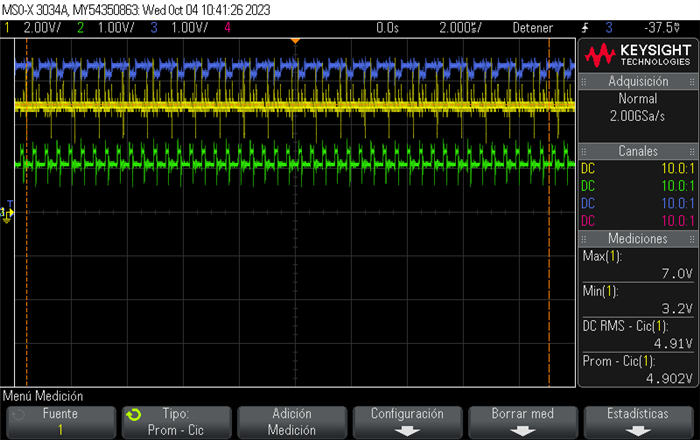

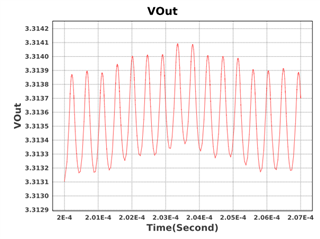

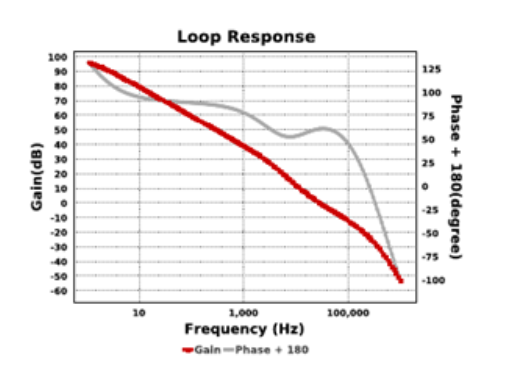

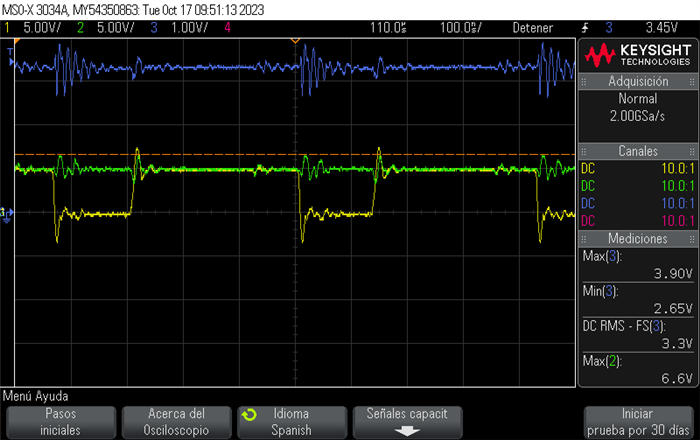

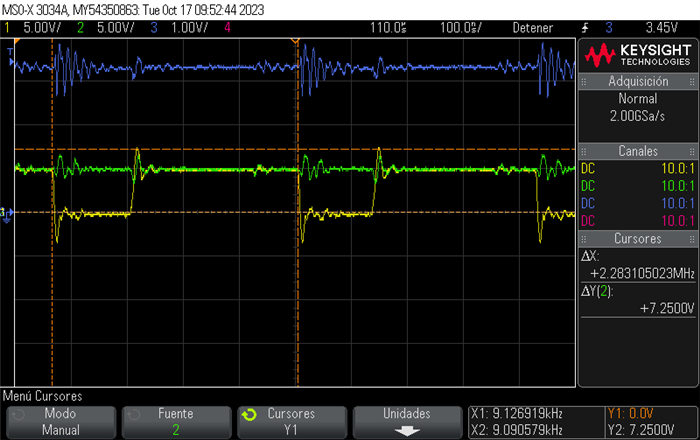

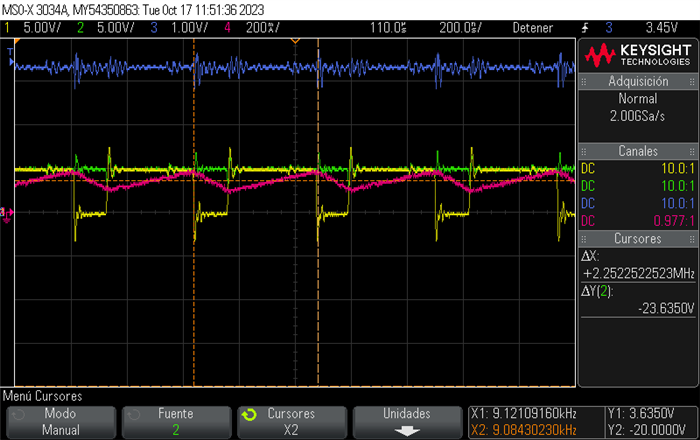

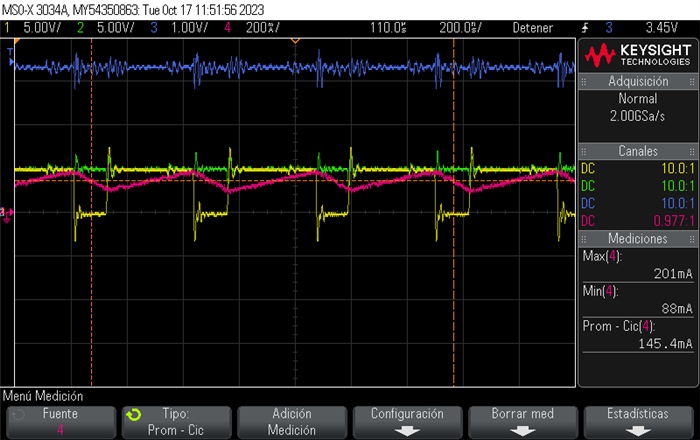

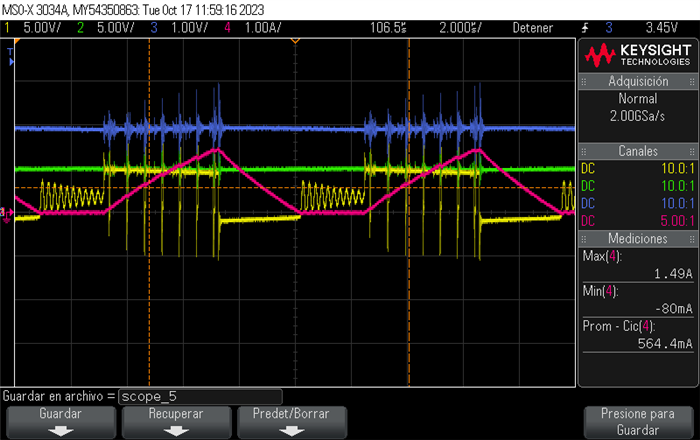

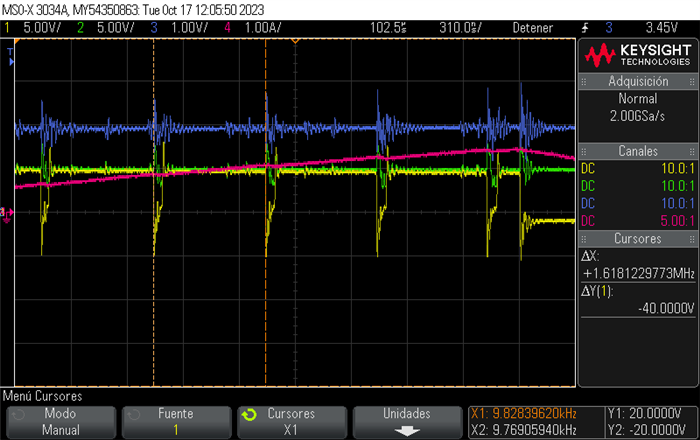

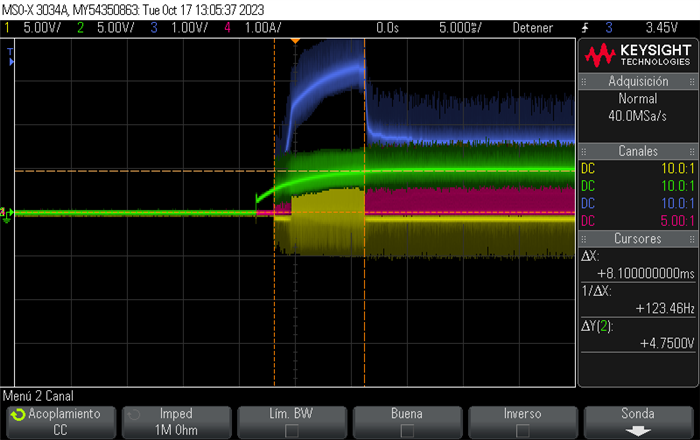

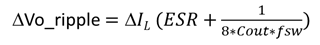

I have the problem that the output voltage has a lot of ripple. Therefore, I need to modify the values of the inductances and the output capacitors to reduce this ripple. However, the LM26420-Q1 is no longer available in the Webench simulator. Could you enable this device in the Webench simulator to develop my LC low pass filter using this inductance and output capacitors?

Best regards,

Francisco.