Hi TI support teams,

I have some question about how to configure the TPS92682 in CV mode & it's SPI communicate also.

I already have a ticket here: Old ticket but that time I need to work on other items so it's closed.

So I'd like to create new one with all my concerns for discussing here :)

So in overall idea, our customer is using the TPS92682 in CV mode to provide 12V output.

1. Could you please help check my configuration here: Are those configuration ok for 12V output? Are there anything that I need to update?

About the value of CHxIADJ, I've follow the equation 44 in datasheet with FB1 resistor = 10kOhm & FB2 resistor = 75kOhm to calculate it's value

EG_EN, 0xB0 // Set FPINRST = 1 Enable every channel setup - B0 EG_CFG1, 0x13 // LH = 1, chanel set to CV mode EG_SWDIV, 0x00 // 00: Division = 2. CHxCLK = fCLKM / 2 FSW= 400kHz EG_ISLOPE, 0x55 // VSLP(PK) = 250 mV EG_SOFTSTART, 0x66 // 0110: Division factor = 16 for both channel EG_PWMDIV, 0x01 // 01: PWMCLK = CLKM ÷ 2 EG_CH1PWMH, 0x03 // Setup PWM width EG_CH1PWML, 0xFF // Setup PWM width EG_CH2PWMH, 0x03 // Setup PWM width EG_CH2PWML, 0xFF // Setup PWM width EG_ILIM, 0x5F // 01: ILIM event counter threshold = 4, 11: VILIM(THR) = 250 mV EG_IFT, 0x0A // 10: ILIM Fault Timer maximum count = 16 EG_MFT, 0x33 // 0011: Main Fault Timer maximum count = 2000 EG_FEN1, 0x3F // CHxFBOEN, CHxOVEN, CHxUVEN set - Fault enable for FB pin open fault, output OV, output UV EG_FEN2, 0x0F // CHxILIMEN, CHxISOEN set - Fault enable for ILIM fault, ISN pin open fault EG_OV, 0x44 // 100: OVTHR = VFBREF×(1.100) - Factor 1,1 for both channels; max 45V EG_CH1IADJ, 0x96 // Equaltion 44 calculation - 12V output EG_CH2IADJ, 0x96 // Equaltion 44 calculation - 12V output

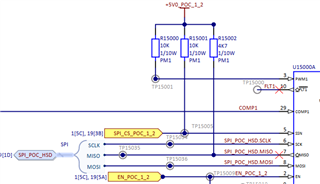

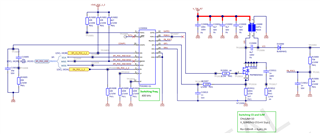

Here is my schematic also

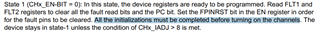

2. I've check the datasheet and the document sluaac4.pdf

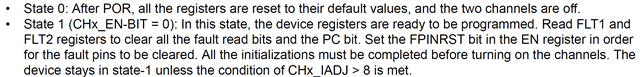

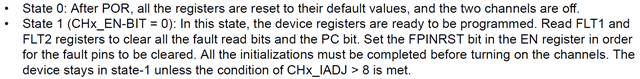

My concern is about when we need to set the EN register value and when be need to read the FLT1, FLT2 register?

It's a bit confuse with me. I'm not really sure about what are actions of initializations step. Can you give me the details information and order of those actions?

What is initializations the datasheet mentioned?

Which order is correct?

Read FLT -> Set EN bit -> Write to registers to config

OR

Set EN bit -> Write to registers to config -> Read FLT

OR

Read FLT -> Write to registers to config -> Set EN bit

Are there any delay need in each action?

3. SPI read/write issues

To write the config value to the resisters, I created a driver under Linux to do that.

But it seems that the SPI communication has some issue and I still cannot write or read the registers. I'm not sure it's my software issue or about hardware configuration issue.

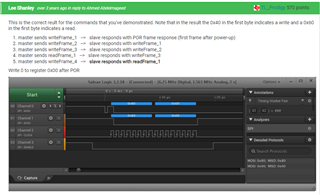

I follow the instructions here to perform some write/read actions to verify the SPI communicate: tps92682-q1-what-would-be-the-response-frame-in-case-of-write-frame-following-read-frame

For example:

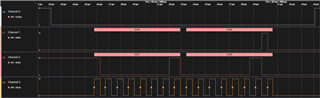

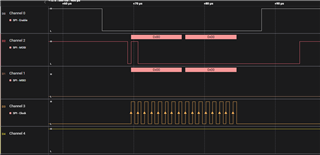

This is the expectation of first frame follow about ticket:

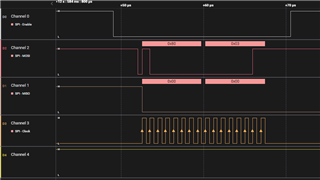

With mine, I can see that I have the same command packet on MOSI line, but the value of MISO seems not correct.

Write 0x00 to register 0x00 after POR

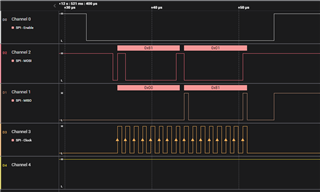

Write 1 to register 0x00

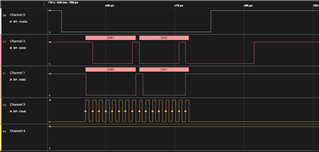

Write 2 to register 0x00

Read register 0x00

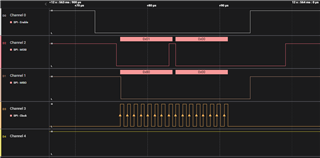

Write 3 to register 0x00

And these are all the view of 5 frames

Note: The Channel 4 is the EN pin of the TPS92682

Could you please have take a look on this to see if there are anything wrong? Can it be the hardware configuration issue because I can see that the frame value seems correct?

Best regards,

Loc.