I've previously brought this question up in a different thread regarding the LM74801, and use of the LM74810 was recommended by Praveen as a solution because of the linear comparator's ability to block reverse current. See this thread for reference:

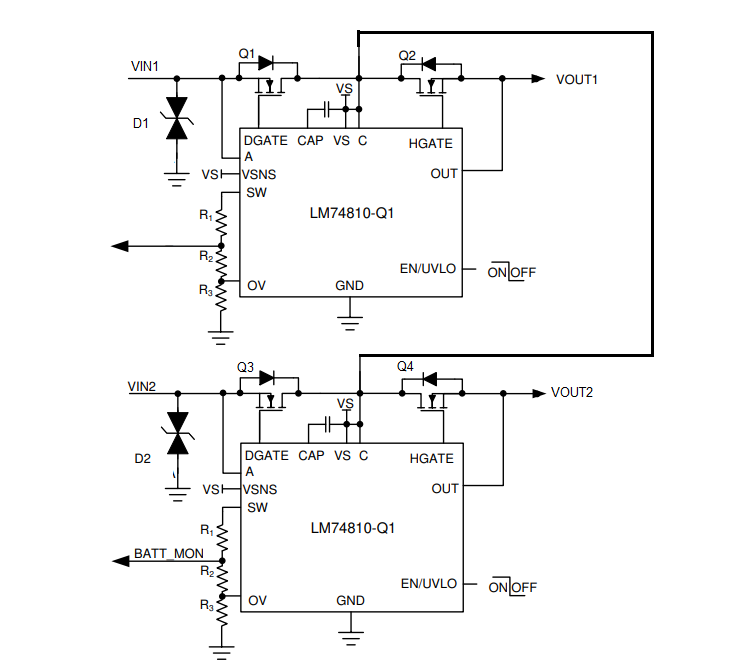

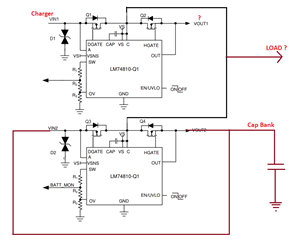

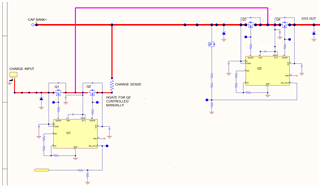

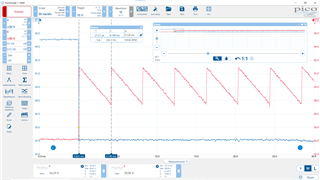

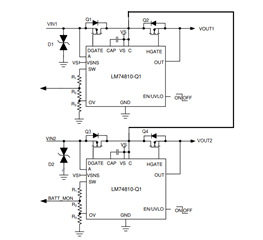

I have since respun my board, this time with the LM74810 instead of the LM74801. My circuit is for a cap bank charger that uses one 74810 to control the charge current, and one to control the output, and they are ORed together similar figure 8.6 on page 17 of the datasheet with the exception that the upper controller has both FETs and they're ORed at the common drain point. Please reference the figure below as a representation of my circuit since I am not permitted to attach a schematic:

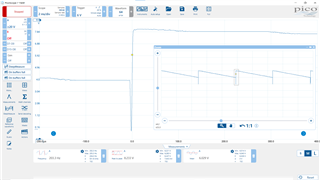

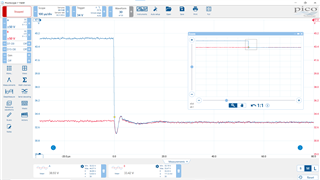

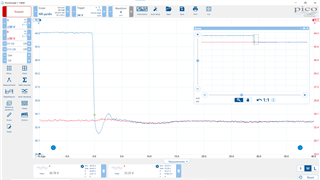

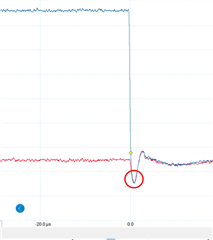

I use the upper controller to switch the charge current on and off, and VOUT1 current is monitored, as well as the voltage. When the charge voltage required is reached, a microcontroller shuts off the HGATE of the upper controller. The probelm I have with this is that the current flowing backwards through Q3 should be sufficient to shut it off. RDSon for Q3 is 1.5mR, and when the system is running, it is most likely that current is also flowing out of Q2 and backwards through Q3 simultaneously, but Q3 is not turning off. I've had everything from 0.1A to 5A flowing backward through Q3. Should this be turning off or is there something about the linear amplifier circuit that I missed that prevents it from turning off? This poses a significant problem, and if the recommendation from Praveen to use this part was incorrect, I need to know ASAP so I can remove this part and find a different solution.