Hi TI,

I have two quwstions.

Question1:

GPIO9 is used as PGOOD in order to monitor with other devices that the PMIC has completed power output.

PGOOD is outputting H regardless of the state in which BUCK/LDO is not output (0V).

It has remained high ever since VCCA/VIO was turned on.

I understand that PGOOD=H if the output voltage is within the OV/UV threshold, but is this correct?

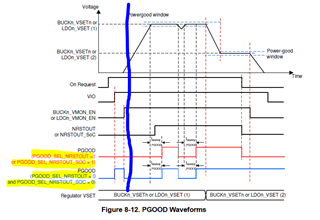

H/L does not change as shown in Figure 8-12.

Address setting are follows:

0x078 0x02

0x079 0x00

0x07A 0xAA

0x07B 0x88

Question 2:

The PMIC is accessed from the control device via the I2C bus (without CRC).

I am able to write to the register without any problems, but the PMIC is returning a NACK.

Reads the written register and confirms that it was written correctly.

Can this NACK be ignored? Or should I treat it as an access error?

Please let me know if there is any other information needed for analysis.

Thank you.