Hi TI Folks,

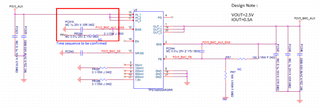

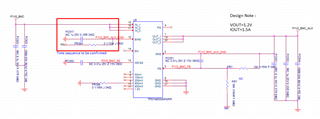

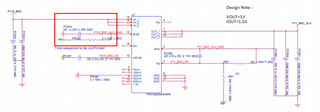

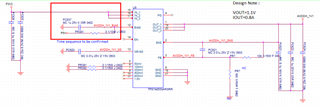

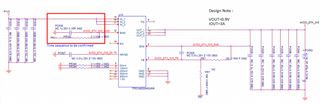

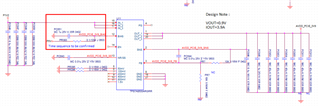

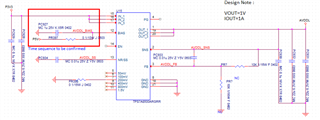

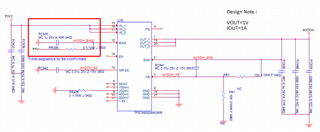

My case uses TPS7A8500ARGRR, please help to check the schematic design. (The voltage and current are written in the design note)

Especially Vdrop and thermal evaluation.(Vn VS Vout)

On the other hand, May I ask VBIAS under what circumstances should I pull high? Is a pull high resistor needed?