Hi Team,

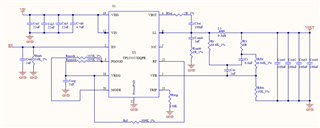

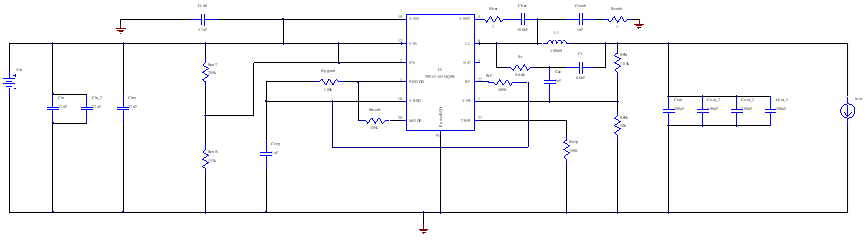

The TPS53355 in the circuit is used under the following conditions: VIN=12V, Vout=1.03V, Iout max =20.4A.

And the design is as follows:

Note:

a. All capacitors in the above figure are ceramic

b. L1 has a DCR of 1.06 mΩ

c. FSW=750kHz

Issues:

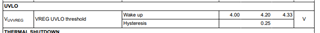

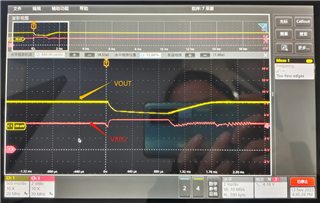

1) Some chips output about 0.5 V after power-up when at cold temperature -40°C, while it will only output the nominal voltage of 1.03 V after a few seconds. The output of the chip is good at normal temperature.

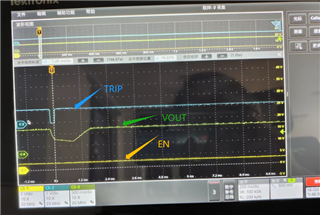

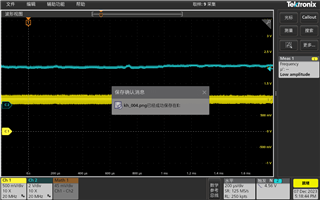

The waveform is as follows:

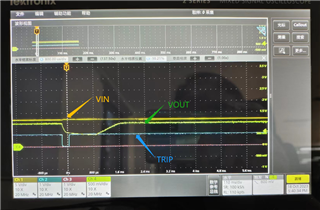

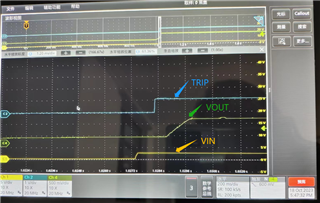

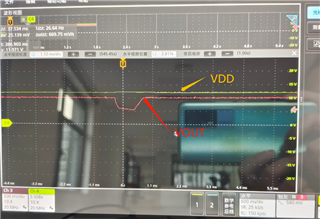

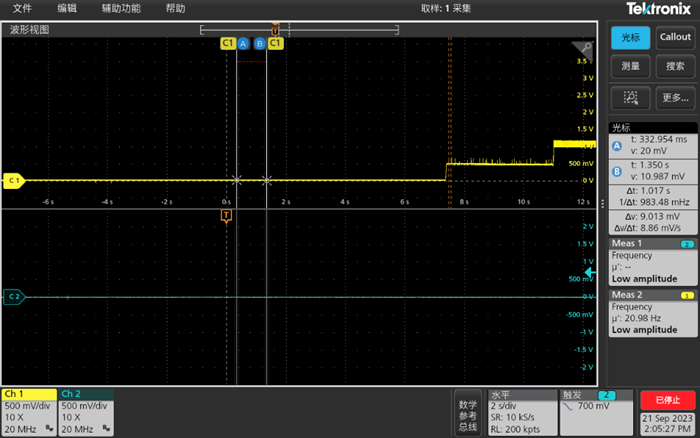

2) Some chips have dropped after a period of power-up when the temperature is -35℃. The waveform is as follows:

However, the chip can start up normally at low temperature -30℃. The TPS53355 output voltage is not proper, causing the system cannot start at low temperatures.

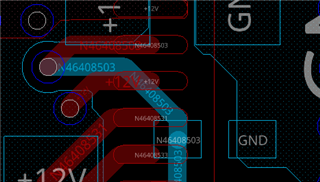

3) If the Csnub and Rsnub of the LL pin of the chip are not soldered or have wrong parameters, the chip output is only about 0.39V and cannot output the nominal voltage of 1.03V.

And the customer has tried the following but there are no improvements:

- Modify the Rr and Cr parameters of the ripple injection circuit to be close to L1/DCR(L1=330nH. DCR=1.06 mΩ) or decrease the DAC to 680 pF.

- Modify the inductor value to 550nH or 160nH, other parameters are unchanged.

- Increase capacitance, increase Cbst to 220nF, increase Cfg to 10uF, Cin adds two 22 UF capacitors and Cout adds two 100 UF capacitors.

Could you help look into the following problems:

1) What parameters does low temperature affect the TPS53355? How can these effects be reduced or eliminated?

2) Could you please help review which parameters in the circuit need to be modified?

3) What is the role of Csnub and Rsnub for the LL pin of the chip? Why does it affect output when not soldering or when parameters are not correct?

Best Regards,

Cherry