Other Parts Discussed in Thread: LM74900

Hi,

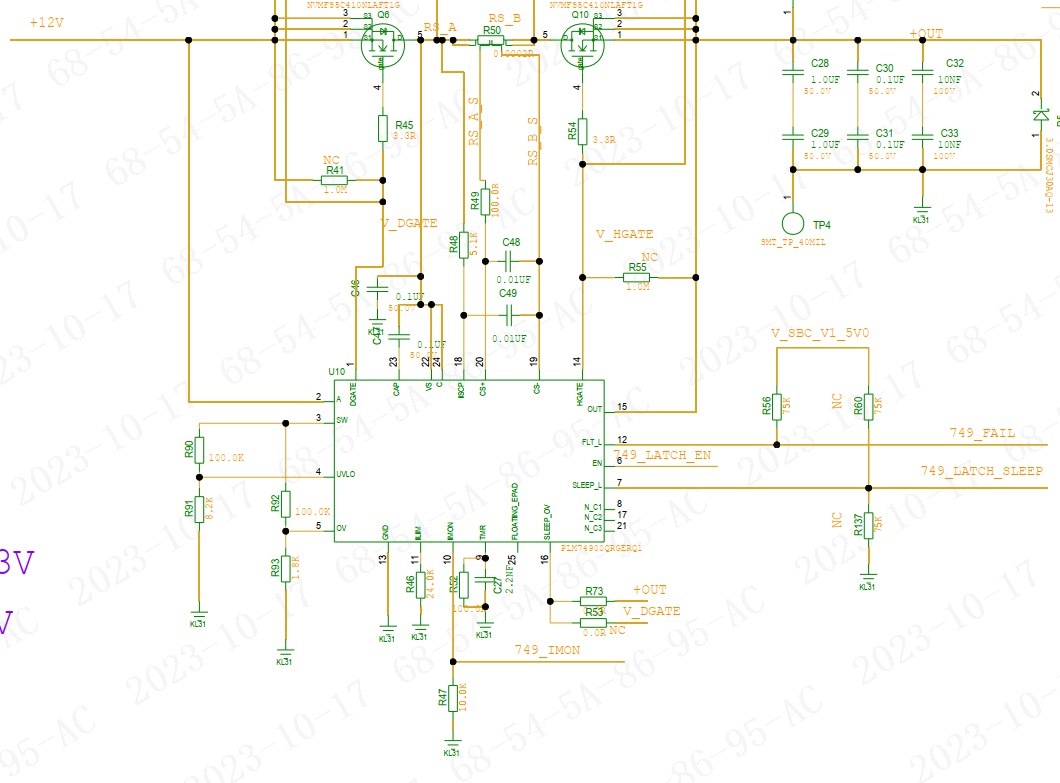

My customer is facing a problem when using LM74900, which can be described as following:

The input (Vbatt) is set as 13.5V, EN is pull-up to 5V, and /Sleep is also pull-up to 5V, the load is connected with a 100Ohm resistor.

They found that the MOS are both not switched on normally, which can be described as following:

Dgate - VI = 2.2V (normally should be 11. V), the front MOS is switched on, but they think the gate voltage is abnormal.

Hgate - Vout = 0.9V (normally should be 11. V); the right MOS is not switched on.

And the fault pin has no output. Thus, they are wondering which reason can cause this problem.

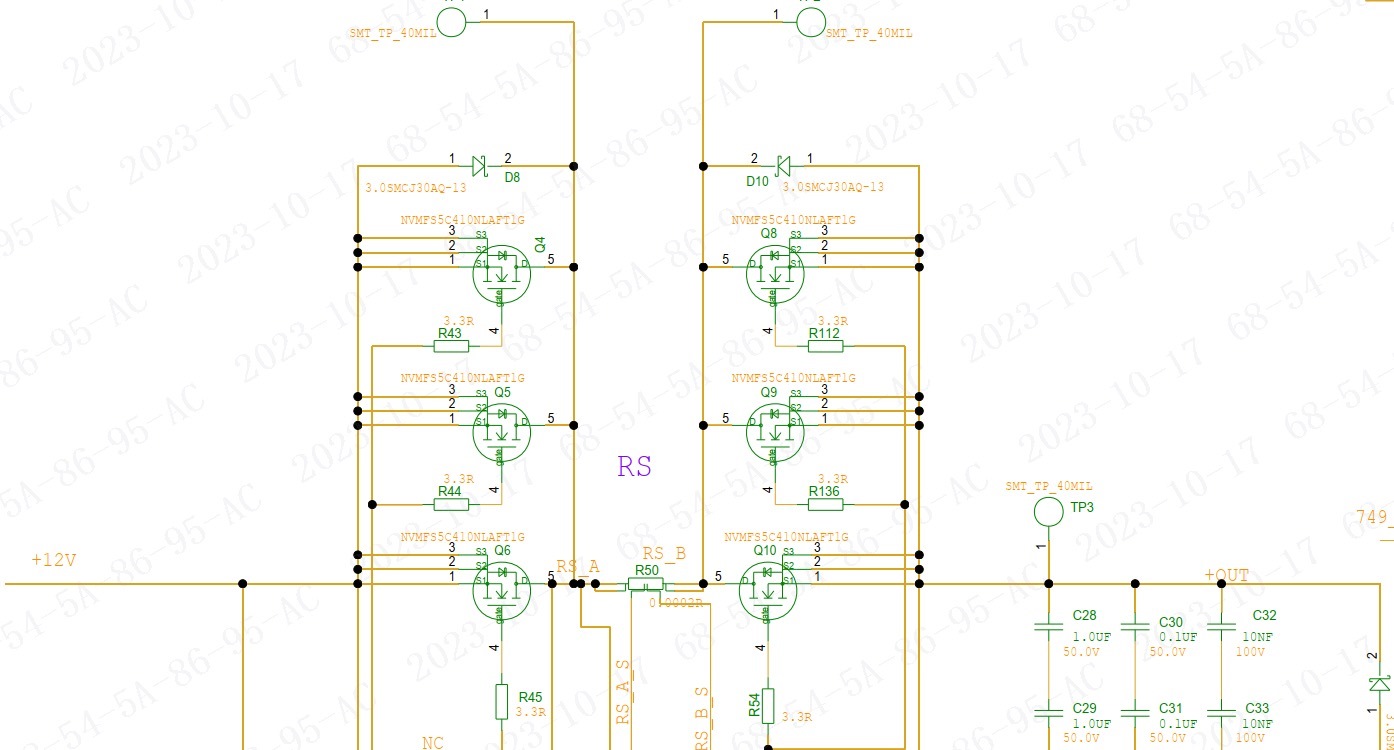

The schematic is given following, which contains the overall picture 1, overall picture 2, upper part and lower part. For the clear picture and parameters for your review.

What's more, in the schematic, the three paralleling MOS are not used in the same time. Although there are three in per channel, actually they only use one, and the gate resistor of the remaining two are disconnected. And the gate resistor of the remaining one is zero Ohm.

Please help check the potential problem in this schematic, which can cause this problem. And help provide the improvement recommendation.

This issue is really urgent, if you do not have the answer today, I hope we can hold a discussion meeting with my customer online, for discussing the potential problems. Thanks!