Hello team,

I am confused how to design CFF configuration. All the designs are different on datasheet, EVM, and PSpice reference schematic.

Which design should I follow?

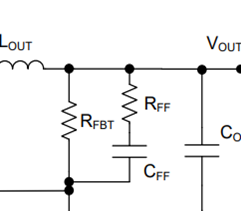

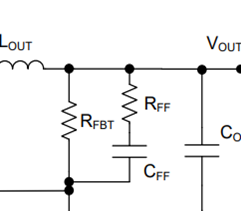

Datasheet

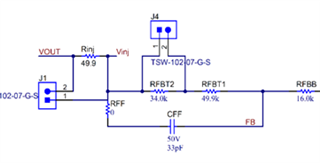

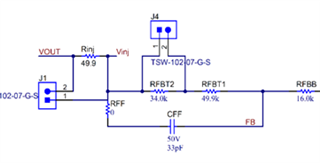

EVM

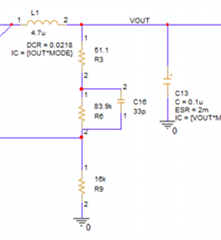

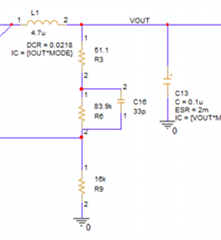

PSpice reference schematic

Best Regards,

Kei Kuwahara

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello team,

I am confused how to design CFF configuration. All the designs are different on datasheet, EVM, and PSpice reference schematic.

Which design should I follow?

Datasheet

EVM

PSpice reference schematic

Best Regards,

Kei Kuwahara

Hello Kuwahara-san,

The datasheet shows Rff and Cff. The Cff is the main contribution to improving phase margin and load transient. Since the Cff can conduct noise from the output of the circuit directly to the FB node of the IC, a 1-kΩ resistor, Rff, can be placed in series with Cff.

In PSpice does not account for real world noise coupling onto FB so that is why it is not included there. The design on the EVM has a 0Ohm placeholder for Rff just in case there is noise coupling onto the FB and causing regulation issues, the end user can place any Rff resistor to help with this.

Note that the Rff is not a must have but rather is a good to have component, so not required unless noise is observed.

Regards,

Jimmy