Other Parts Discussed in Thread: TPS65219

Hi,

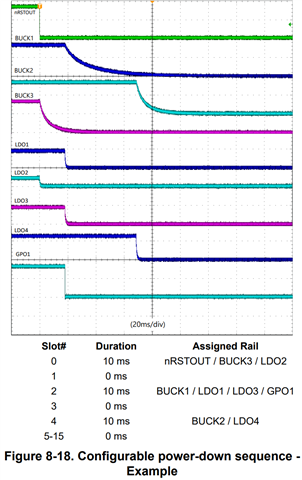

Could you explain below difference between register input and actual results in the datasheet figure8-18?

In below picture, nRSTOUT/BUCK3/LDO2 power down at same time is programmed and it works well.

After 10ms, BUCK1/LDO1/LDO3 power-down is programmed but in the picture, it is around 18ms.

After 10ms, BUCK2.LDO4 power-down is programmed but in the picture, it is around 50ms.

Please let me know how power-down timing is measured.

Thanks.