The block diagram shows an internal ramp generator creating a 0.8V to 2.8V sawtooth for the PWM comparators inverting input.

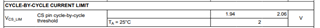

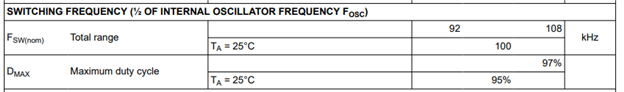

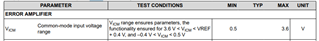

Including the offset voltage and hysteresis of the PWM comparator, what are the threshold ranges for the COMP signal?

In other words, if I have RSUM configured for VMC operation and control the COMP pin voltage (to control duty cycle), what voltage on COMP will create a 0% and a 100% duty cycle? And what are the tolerances of those thresholds?