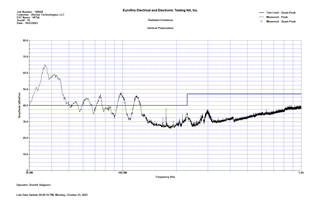

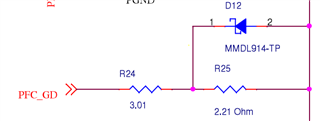

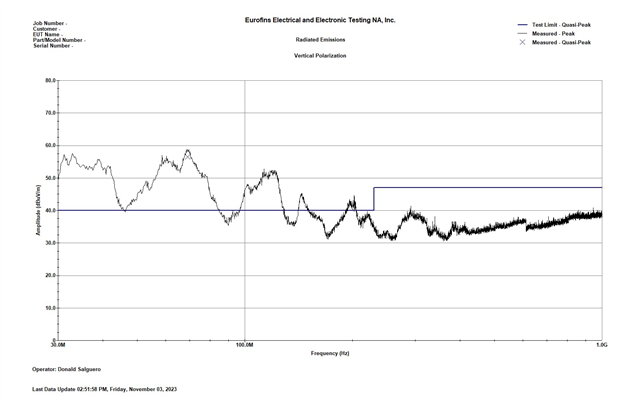

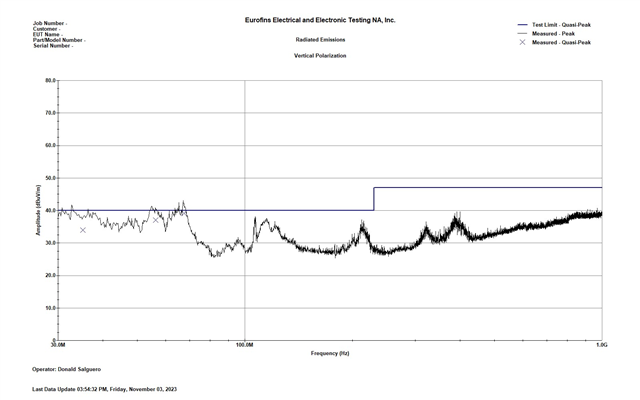

My team has designed a lead acid battery charger using the above part number. We used the evaluation board recommended parts and design. I attached the schematic below. my charger works, however I have EMC issue. As you can see from the attached Vertical SCAN it has major emission between 30 MHz-50 MHz and below 100 MHz in general as you can clearly see in the scan. I have tried ferrites with my AC wires to my board, it did not reduce the emission much. I also tried a mock up shield that did not help much as well. I am wondering how to resolve this problem, I would appreciate any insight to this problem I am facing with my product.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.