Other Parts Discussed in Thread: SYNC-BUCK-FET-LOSS-CALC, CSD18531Q5A

Dear TI Team,

I try to find the best fitting MOSFET's for my design, as we have currently temperature issues during bringup.

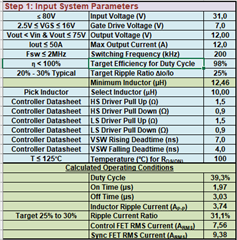

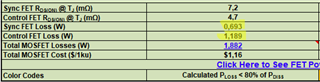

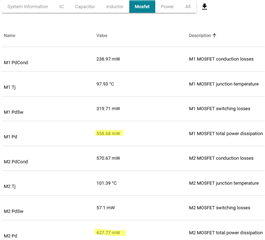

I tried the WEBBENCH and also the Tool "splr001a.zip" (SYNC-BUCK-FET-LOSS-CALC_Rev2.xlsm).

Unfortunately I get quite different results for the Powerloss for both MOSFET's with WEBBENCH or splr001a.zip.

Could you please tell me which of the tools I should trust for the power dissipation calculation?

Thank you very much for your support!