Hi all,

I trying to implement PSFB converter with UCC28950 IC. I am giving 12V bias separately and the input voltage(400V) through a Bridge Rectifier Circuit.

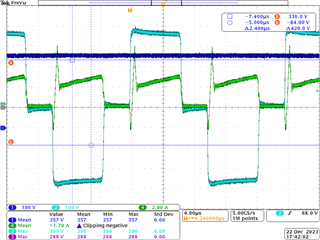

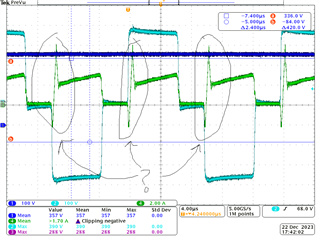

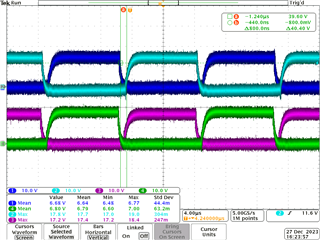

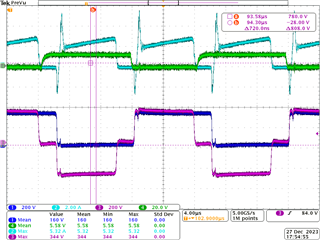

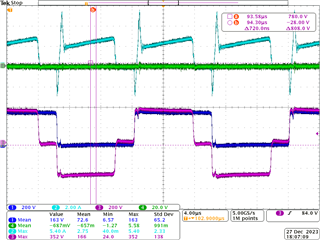

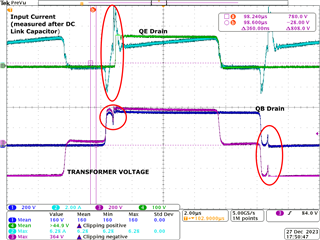

When the bias 12V is given, the QA, QB, QC, and QD are showing pulses of nearly 50% duty ratio. However there are no pulses for switching the secondary devices (QE, QF).

The Vref value is 5V, SS/EN is also 5V.

What could be the issue for the circuit not turning on.

What other parameters need to be checked for troubleshooting.

Thanks

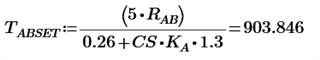

ns

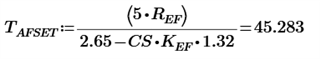

ns ns

ns