Other Parts Discussed in Thread: LM5050-1

Hi team:

My customer use LM5050 for the function of preventing backflow. Would you help to review the SCH and issue?

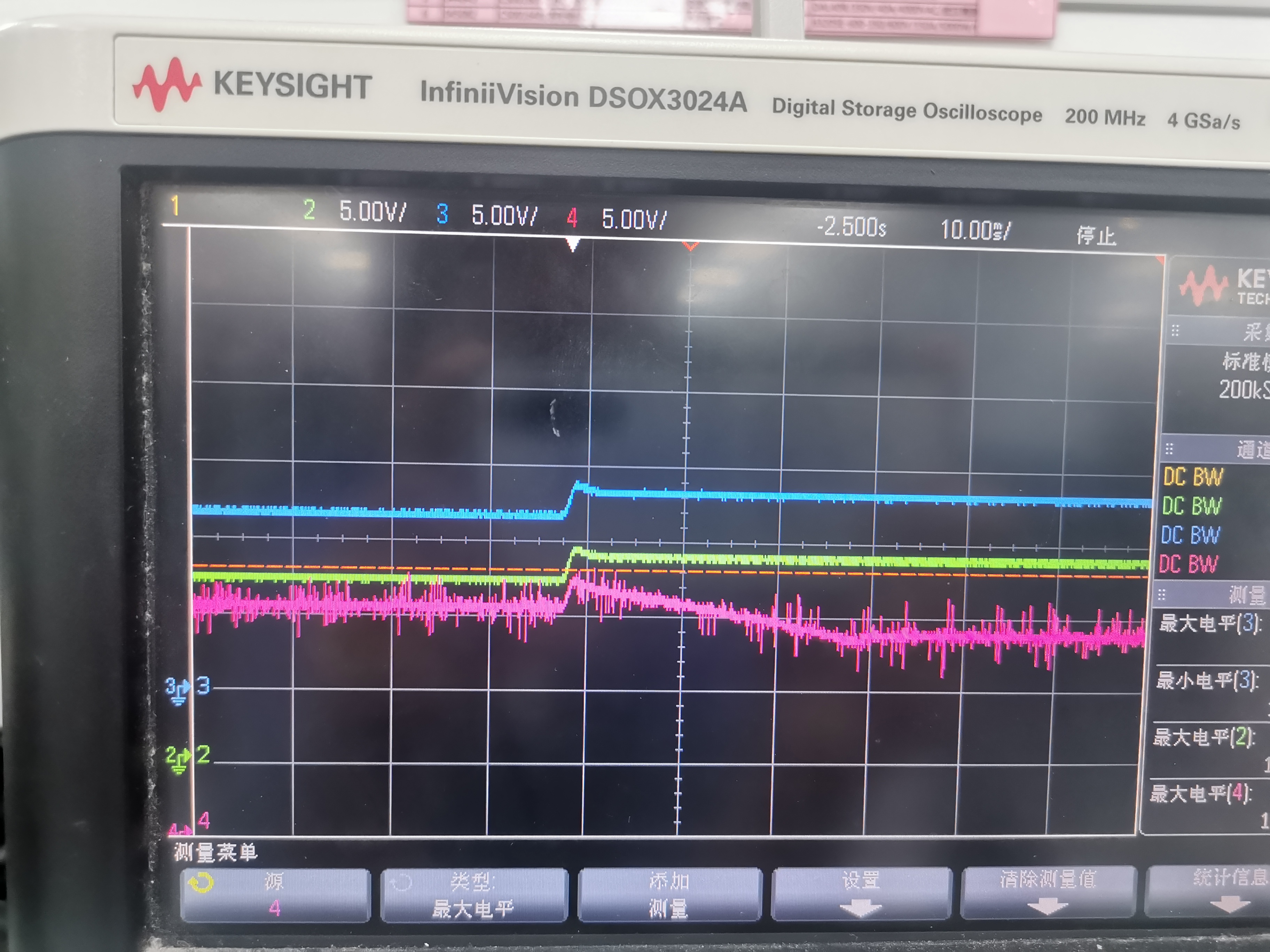

The current phenomenon of the product is that if the output has no load and light load. The backflow function works here . The waveform attached as below:

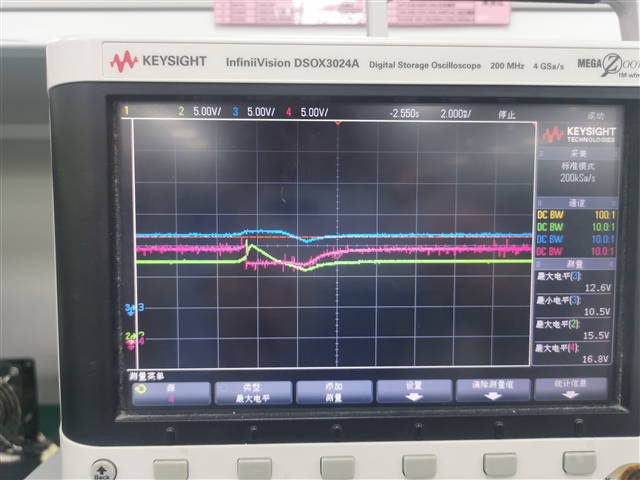

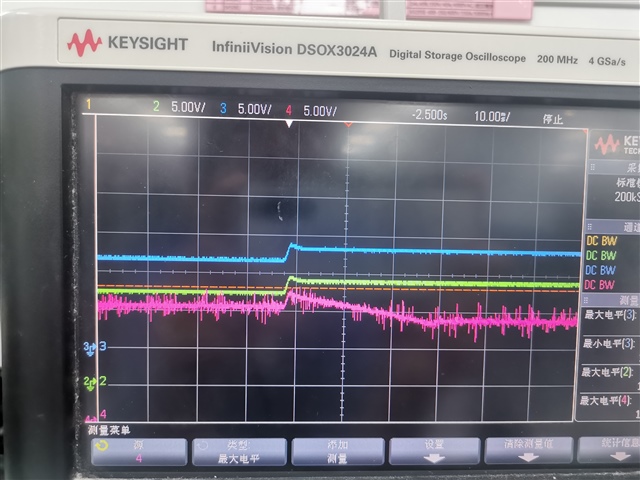

Green is VOUT(6PIN)

Blue is VOPRE(4PIN)

Red is the driver of lm5050(5pin).

But when the product is fully loaded and the output current is increased, The backflow function not works here . The waveform attached as below:

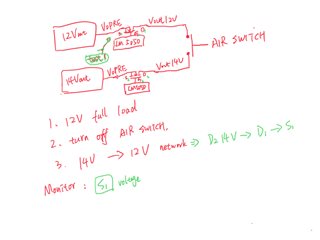

SCH: