Hi all,

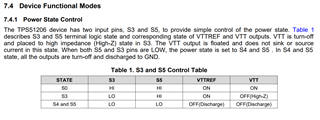

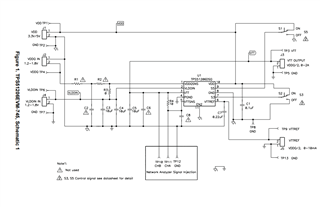

I am investigating the use of the TPS51206 for a DDR4 application at 1.2V logic. Section 7.4.1 of the datasheet lists the power states needed to control the device but I have a few questiosn regarding these two pins:

1. How do you properly terminate the S3 and S5 pins for 1.2V logic?

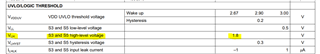

2. What is the proper logic control for DDR4 using the S3 and S5 pins? What voltage levels do the HI and LO states need to be at 1.2V as this is not clearly defined in the datasheet.

Let me know your thoughts whenever possible and I hope to hear back from you soon