Other Parts Discussed in Thread: TPS7A8300, TPS745

Hi,

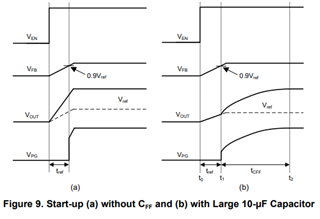

I find Cff will make start-up time longer.According to the application note https://www.ti.com/lit/an/sbva042/sbva042.pdf?ts=1698638510370, it's normal. Though it take TPS7A8300 is used in this example, TPS745 works the same.Green one is VFB and yellow one is Vout.

With Cff, you can see VFB rises and stays at Vref. It seems to have nothing to do with Vout. The application note mention that. "During the tref time, VOUT tracks VFB. VFB is controlled by the LDO feedback loop and is forced to match Vref. "

My questions is why VOUT tracks VFB and how the feedback works if VFB is forced at one voltage level?