Hi expert,

Customer used TPS40422 and setup a test procedure to disable and enable the device by controlling CTRL1 pin only instead of removing the VDD. However they see one board got a problem that after disable the TPS40422, it can't power up again. Below are more detail explanations from customer. Would you please have a look and advise if below questions accordingly?

We are developing a new switch that uses the TPS40422 and have run into an issue on a single system but are concerned that it might be symptomatic of a larger problem.

Our switch requires this supply be trimmed based on a settings from the primary switch chip on the card.

What we do is enable the supply to come up at a nominal voltage, query the switch chip to determine the trimming factor and then program the VREF_TRIM with the appropriate value. We do this every time the box powers up and never write anything back to the PROM.

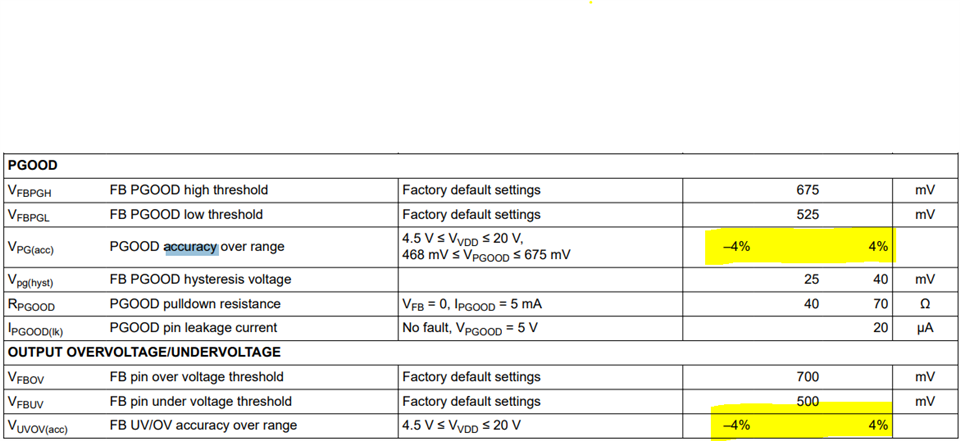

On occasion, we have to power cycle the POLs without a full system power cycle (i.e. without removing the AC power). To the POL this means that we essentially disable and re-enable it using the CTRL1 signal. We leave it disabled for approx. 6 seconds. In this case, presumably because the TPS40422 doesn't lose VDD/+12V, it seems to retain the value of the VREF_TRIM setting. What we see on this one system is that we never get a power good indication, no matter how long we wait. We can also retry this cycle; disable, wait 6 seconds, re-enable, wait for PG, over and over without any success.

On a previous project, we actually did this same trimming in manufacturing and programmed it into the PROM such that from then on, the device always powered up to the trimmed value. This seems to be working fine, but we did notice in MFG that some systems had power good failures when we set VREF_TRIM before writing it to the PROM. To solve this, we set the PCT_VOUT_FAULT_PG_LIMIT to 0x3 before writing VREF_TRIM and this seems to have resolved the issue. I assume we set it back to the default after setting VREF_TRIM but before writing the PROM, so that subsequent power-ons will have the tighter PG_LIMIT (but I should verify this). We also adjust PCT_VOUT_FAULT_PG_LIMIT on the new switch before and after setting VREF_TRIM for this same reason.

So, the result of all this would seem to be that our new switch, after being disabled and re-enabled, would come back up with the trimmed value set in VREF_TRIM and the default value for PCT_VOUT_FAULT_PG_LIMIT. It seems like this is essentially the same scenario as our previous design, even though we haven't programmed the PROM to store the adjustment. But for some reason it doesn't work on this one sample.

To solve this problem on this particular switch, I send a RESTORE_USER_ALL command to the TPS to reload the original register settings after I disable it but before waiting the 6 seconds and enabling it. This seems to be working.

Q1: So, first question is, does this procedure for trimming the supply make sense? Are we doing anything wrong?

Q2: Is our assumption correct that nothing changes in the TPS registers when CTRL1 is toggled?

Q3: Any idea why the supply doesn't come back up correctly after the disable/enable cycle? It doesn't look like the PG_LIMIT causes the TPS to latch up in the failure condition, it seems like it would eventually regulate given enough time but doesn't seem to be doing so in our situation.

Q4: Does the RESTORE_USER_ALL command sound like the right thing to do or is there a better way to put the TPS back into its default state? Does that reload the entire register set?

Q5: One additional thing I noticed recently is that the default value for the PCT_VOUT_FAULT_PG_LIMIT is actually 0x1 not the 0x0 that is in the spec. Is that correct? That looks to be the tightest PG window.

Thanks,

Allan