Hi

Permanent Fail:DFETF:OFF Threshold : -50mA

Permanent Fail:DFETF:OFF Delay : 5 sec

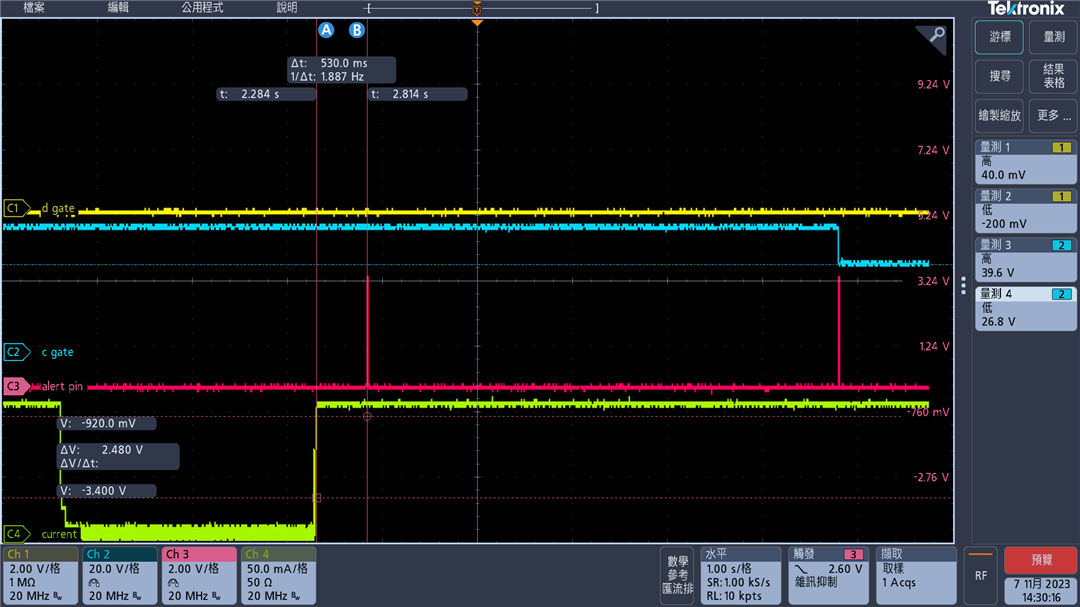

My approach to testing DFETfail

1. Turn on BMS

2. Adjusting the B+ voltage causes UV

3. Use power supply to simulate -60mA at SRP and SRN

4.Watch whether DFETfail occurs

As above method, I can see DFETfail happening

But I receive DFETfail bit between 5.4~5.8 seconds

Is there any way to explain that protection does not occur in 5 seconds?

No other protection I tested, OV UV, had such a long delay.