Hi:

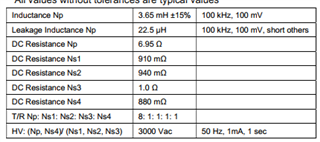

I have a question about the selection of Rcs and Lp.

In my design, the Lp calculated by sluc487b is too large. This will make the volume of the transformer large. If I choose a smaller Rcs I can reduce the value of Lp.

So I want to know what the shortcoming of this is? Will increase the peak current of the primary side? making the duty cycle very low? making the output ripple increase? and are there any other problems?

How should I make a choice?

Thank you very much, You've helped me a lot.