Hi,

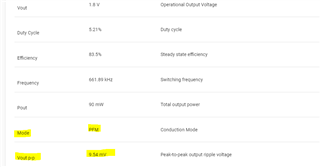

The datasheet for this part family slows a ripple plot for the device in PWM mode.

It makes a statement that in PWM mode ripple is minimized.

It indicates that adding decoupling can minimize the increase in power saving mode but does not quantity this.

Do you have any information about how much more the ripple there will be in power save mode?

I want to use this supply to drive the VDD of a microcontroller with tight supply tolerances.

Is this device suited for applications like microcontroller core voltages where current demands may change rapidly?

Thank you,

Jennifer