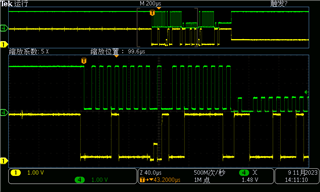

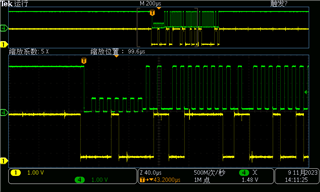

Hi,TI team, we use BQ76952 to design a BMS For 48V battery, and confirm that this chip is the default I2C without CRC. After the overall power-on, we send 0x10 read command to the chip by simulating I2C communication through IO port, and no ACK response is found. Even the SCL level was clamped to about 1.1V in the first few cycles (the chip power supply was 3.3V), and it was found through the simulation device that the single-step simulation showed that the clamped cycle time was variable, sometimes 3-4 clock, sometimes longer, but after that the SCL output level was normal, and no rule was found in this multiple tests. Repeat sending 0x10 for many times and there will be an ACK at some time. However, SCL will be lowered again when the following steps are followed by writing the address of the register that you want to operate, and no ACK response has been checked

the chip wake-up state. During the communication process, the REG18 waveform is measured synchronously and the level is maintained at about 1.81V.

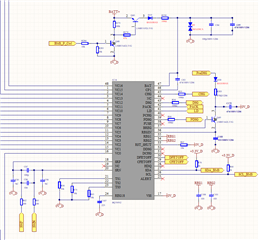

The schematic design is as follows:

CH1:SDA CH4:SCL

The following is the 0x10 write exception:

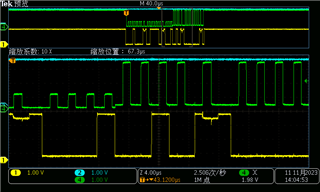

In the following figure, an ACK is available after send 0x10, but subsequent exceptions occur: