Hi,

I am designing a buck to convert 9v~32v DC input to 4.5v. Max. load is about 20w, which means max load could reach around 4.5A.

System load of my product may be dramatically changed from <500mA to max. load so the voltage drop is most concerned.

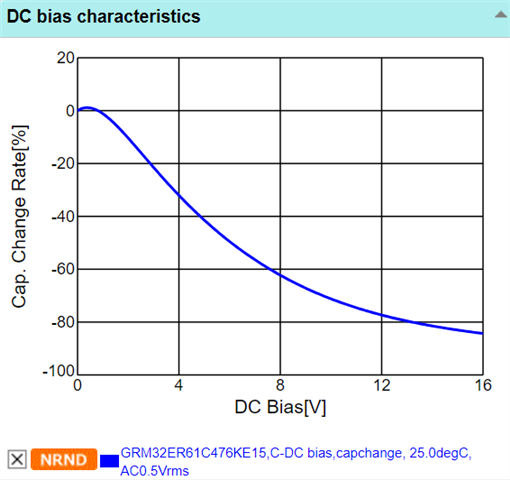

Currently I am worried about the output capacitor selection because I don't want to use tantalum (too expensive). But because ceramic's capacitance decreases with DC BIAS rapidly(I can see a 47uF/16V capacitor drops around 60% of its capacitance under 4.5V) which make me wonder how to fulfill the output capacitance requirement by ceramic caps.

Do you have any suggestion on this?

Thx a lot in advance.

Brs/Sen