After finishing successfully from sending write frames to initialize TPS682, We sent Read frame request to register (FLAT1) to check PC bit.

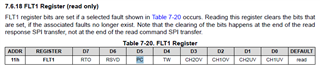

We have sent read frame periodically (20ms) in Normal Mode, but noticed that sometimes 'PC' bit was set even power supply input for the TPS is 8V.

It is confirmed by your side that the PC(Power Cycled) bit is set only when VDD rising threshold(max. 4.1V) is reached at power up.

Also after VDD reaching 10V and assume PC was detected , We sent re-init frames to the chip but Loads were flickered.

So please

1- How can we detect PC successfully?

2- Which frames should be sent after detecting PC ?

3- How to prevent Loads flickering ?

Best regards