Hello,

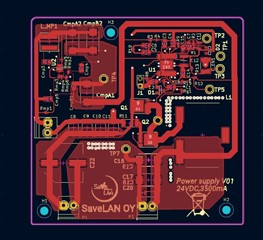

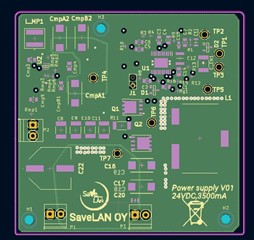

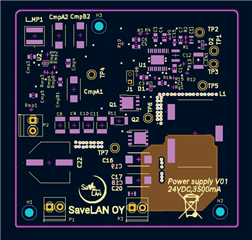

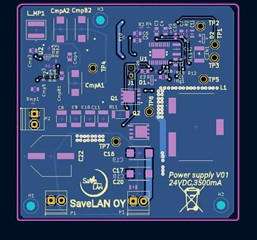

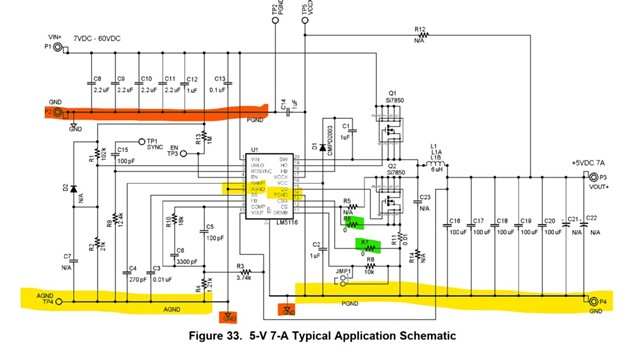

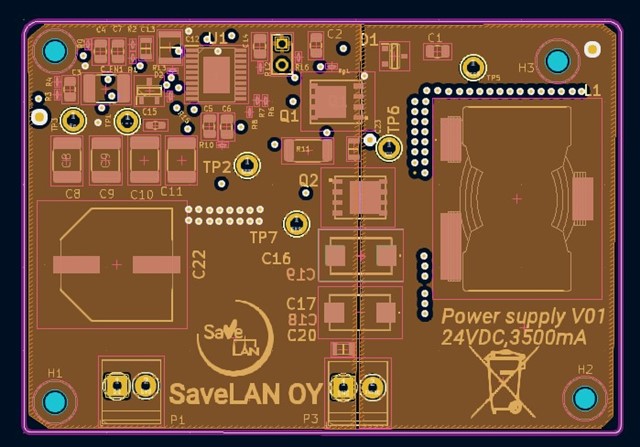

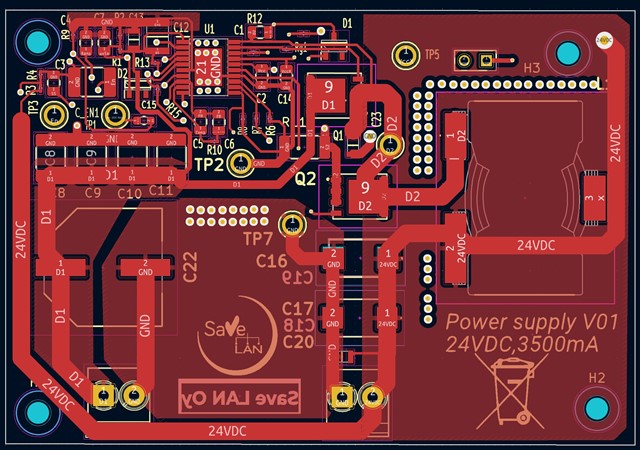

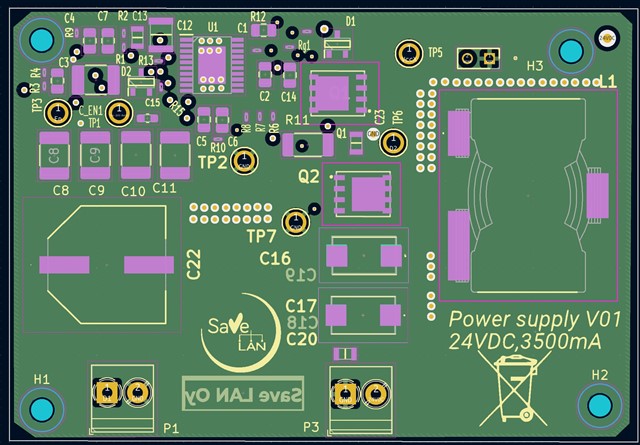

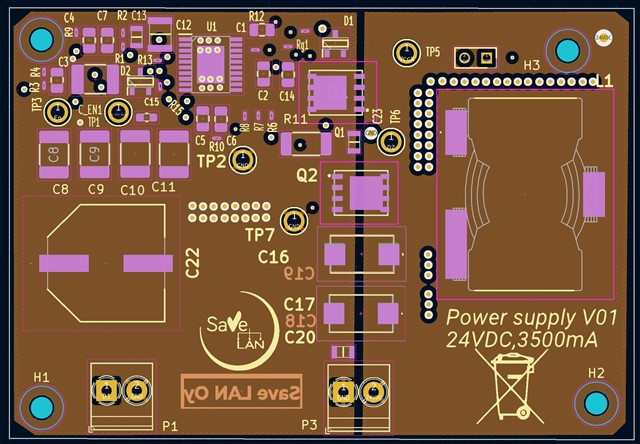

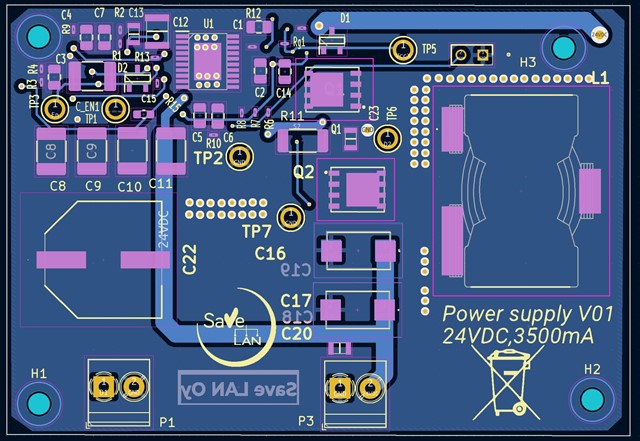

Based on the TI user guide for PCB stack-up designing for LM5116(www.ti.com/.../snva285) I defined 4 layers of PCB for it with these features (2-ounce copper top and bottom, 1-ounce copper internal layers on FR4 material with a thickness of 0.06 inches),

I want to know if is it good to a stack-up layer like below:

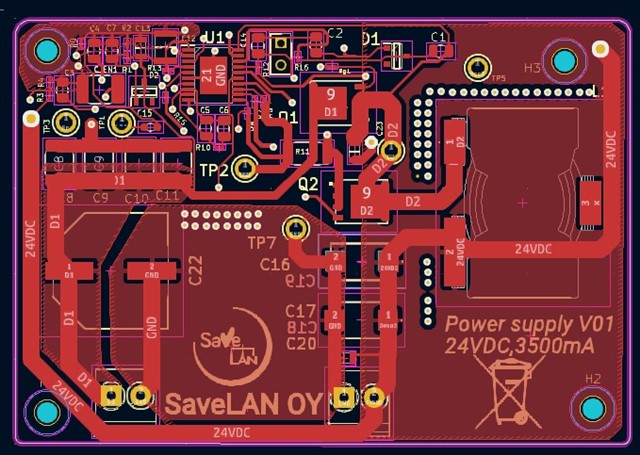

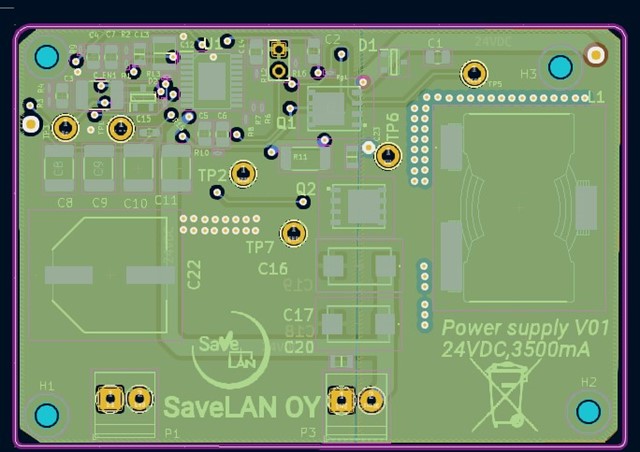

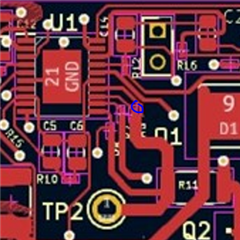

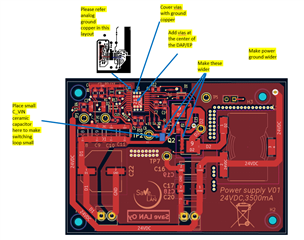

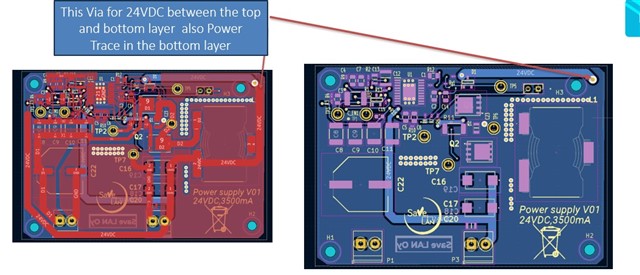

Top: signal ( I created some fill zones based on the PCB layout template in the datasheet )

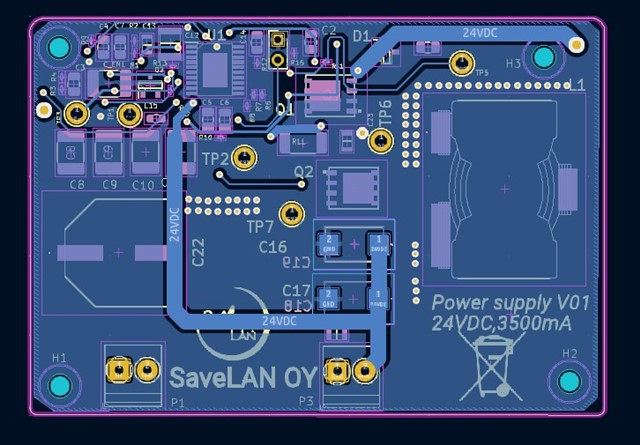

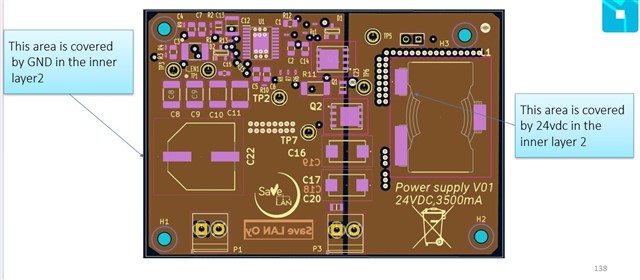

Inner 1: GND

Inner 2: 24VDC ( I designed a buck converter with 40 to 60volt input and 24volt with 3.5 A output)

Bottom: signal ( I covered it with a fill zone that connected to the GND net)

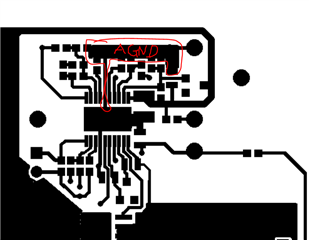

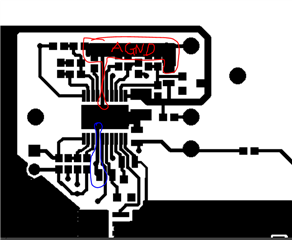

Also, currently, I connected PGND and AGND to GND in PCB. Is it right?

Thank you

Leila