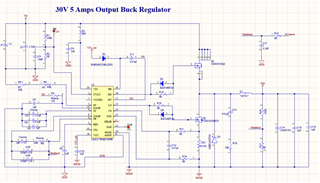

Other Parts Discussed in Thread: CSD19505KTT, CSD19538Q2, CSD18536KCS

I am working with the LM5117 and i have failed to get the output signal to the FETS.

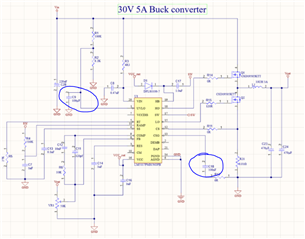

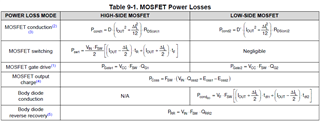

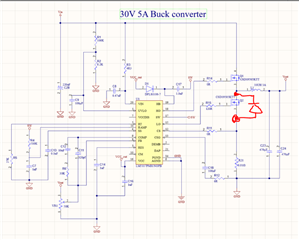

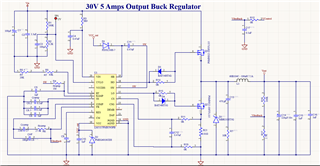

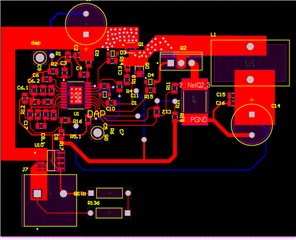

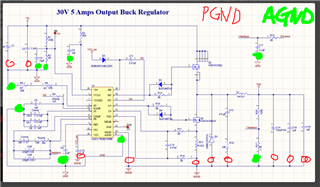

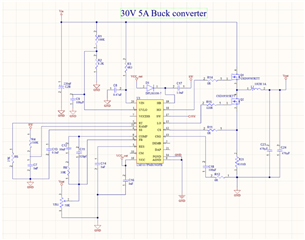

Below is my circuiit diagram with values computed with the LM5117 Quick calc spreadsheet.

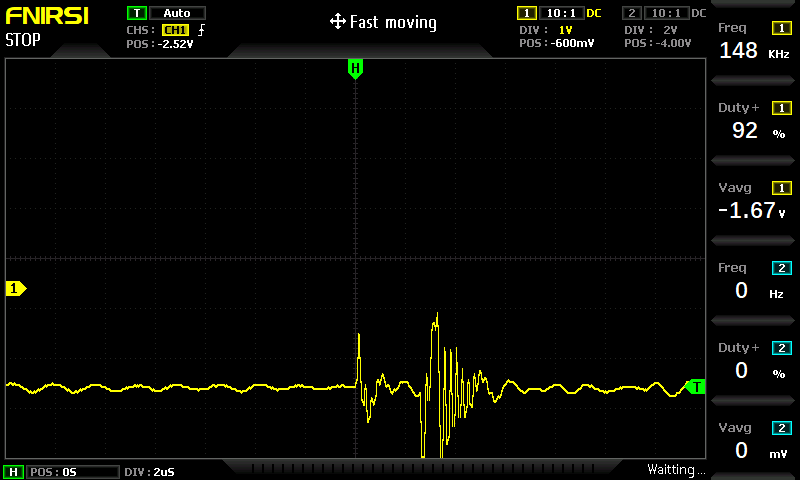

I have measured the following volatges UVLO - 2.5V, RT - 1.2V, SW - 5.3V , VCC - 7.4V, RES, 0V and SS = 0V

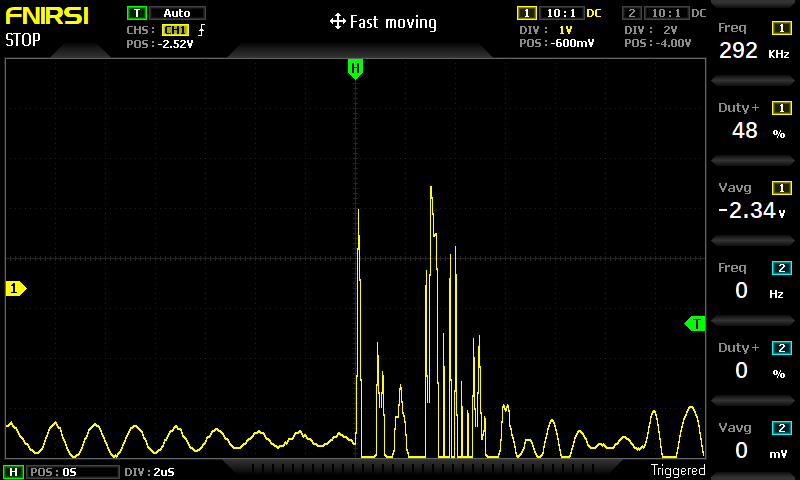

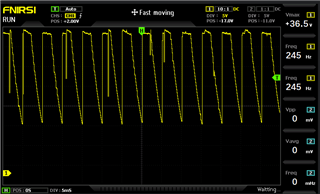

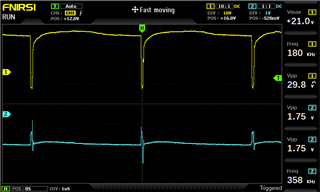

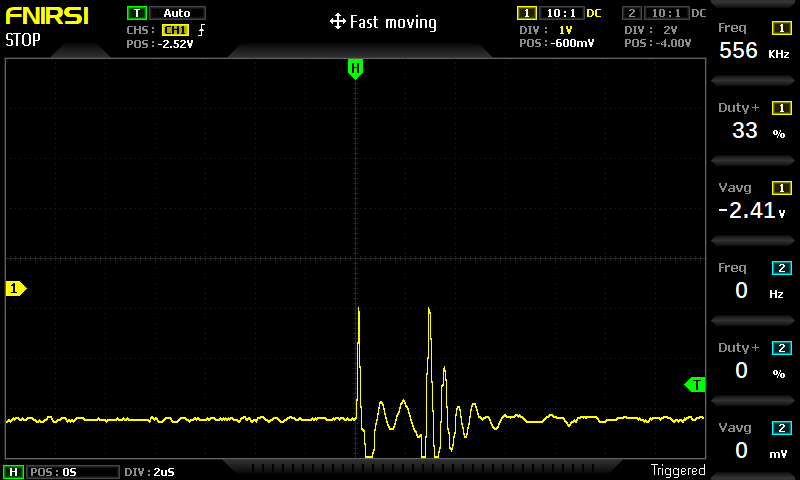

Below are the scope shots showing behaviour at some pins.

HO

LO

RES

SS