Good morning, I'm building a PFC CCM with your UCC28180 integrated circuit.

These are the rough specifications

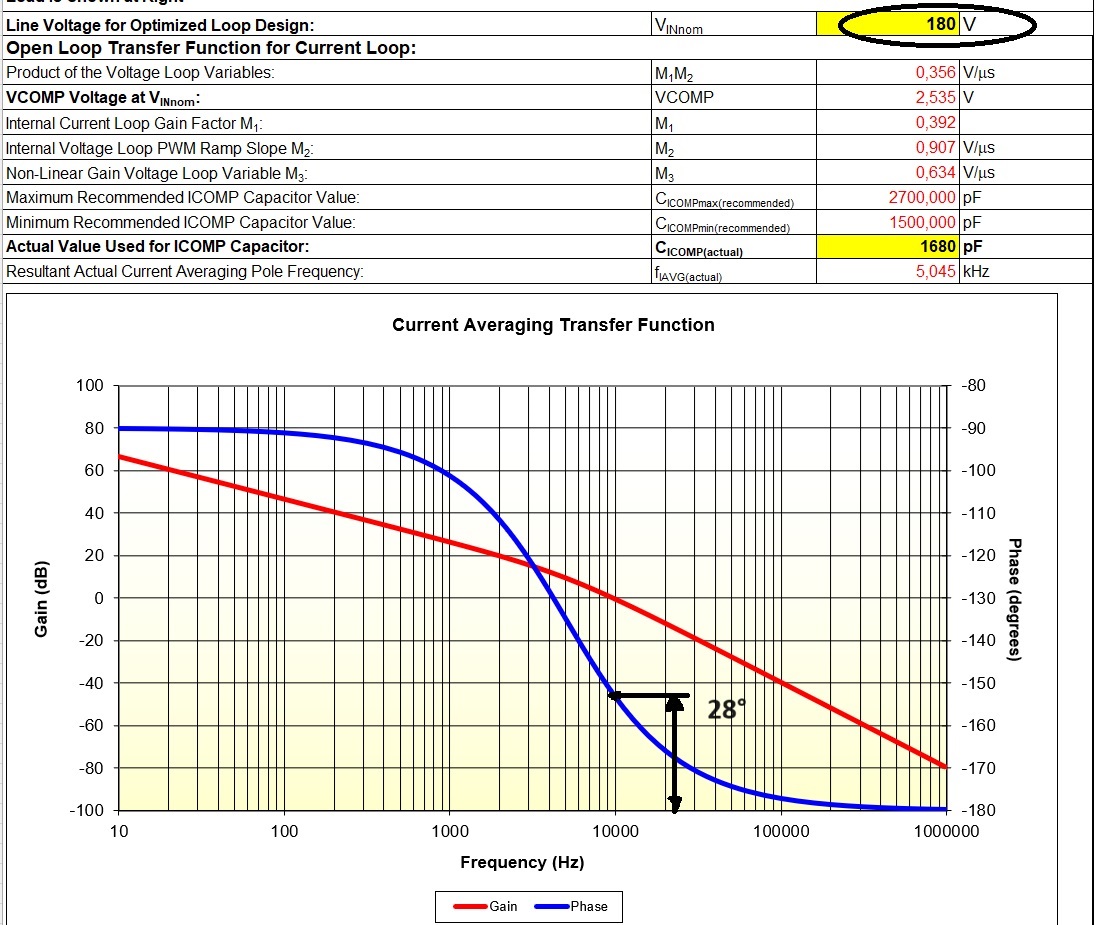

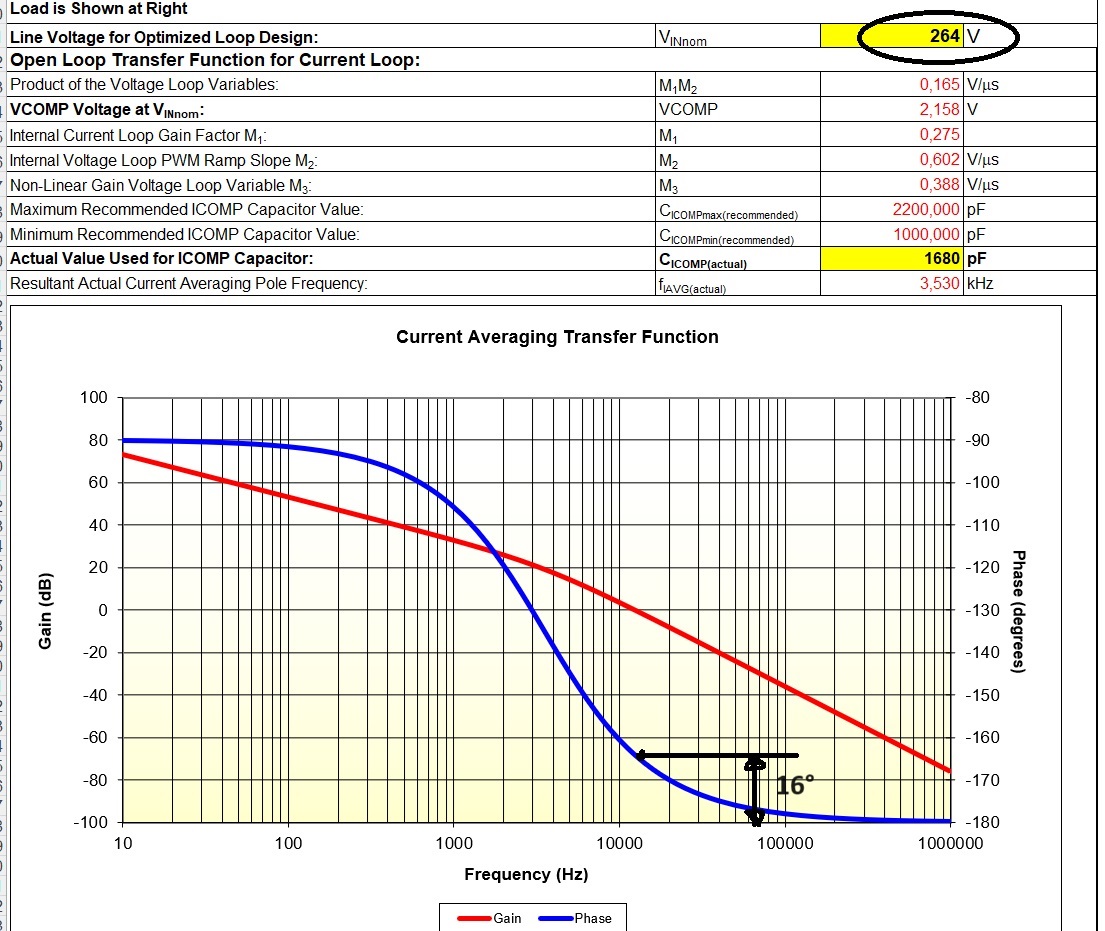

Vin = 180-264V

Vout = 400V

Iout = 2 A

fsw = 110 kHz

L = 250 uH (with 40% ripple peak to peak)

I'm sizing the feedback systems with your excel calculator.

In sizing the current feedback I am finding phase margins of 16-28°.

I wanted to understand if it is normal to find such low phase margin values.

I am attaching both the values set in the excel file for Vin_max = 264V and Vin_min = 180V and the corresponding graphs

Until now I have designed only the control of the voltage loops of buck converters where the phase margin is acceptable only if it is greater than approximately 60°.