LM5143A-Q1 does not start when provide power.

Design: single output / 2-phase. Vin: 24V ~ 50V, Vout: 12V

Pin conditions: VCC is 5V, EN1/EN2 are 5V, SS1/SS2 are 5V, HB1/HB2 are 5V.

The device does not drive the FETs at all. Both Outputs are 0V

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

LM5143A-Q1 does not start when provide power.

Design: single output / 2-phase. Vin: 24V ~ 50V, Vout: 12V

Pin conditions: VCC is 5V, EN1/EN2 are 5V, SS1/SS2 are 5V, HB1/HB2 are 5V.

The device does not drive the FETs at all. Both Outputs are 0V

Kang,

Please attach quickstart calculator and full schematic for this design.

Maybe FB is pulled up or COMP is pulled down incorrectly, or the bootstrap is not setup correctly.

Let us know.

-Orlando

Just realized that I probably need to reply here not directly to your email.

The startup issue was resolved. That was due to a wrong cap value on the DITH pin.

Now the problem becomes:

Kang,

There is insert option in the E2E, use Insert -> "image/video/file" or simply drag and drop.

-Orlando

Is there EN voltage and no VCC voltage?

That appears like VCC regulator has been damaged.

Did you have VCC voltage coming up to 5V before?

Please attach request files.

-Orlando

When it's not starting, VCC is 0V before apply external 5V to VCCX.

When it starts, VCC is 5V. VCC and EN are still 5V even when it goes into some kind of protection, in which the output voltage is almost zero.

That seems that the internal VCC regulator is still good.DCDC_ASK_sch.pdfLM(2)5143-Q1 quickstart design tool - revB3_KL.xlsm

The external 5V to VCCX is applied momentarily to jump start the chip. After starting, there is no need for off-board 5V source.

Increasing the input voltage to around 50V makes the chip going into some kind of protection even with only 0.1A load. The output shuts down. decreasing the input voltage back to around 20V, the output comes back to the regulation at 12V automatically.

Kang,

No jump start should be required, VCC is just an LDO from VIN. Therefore if VIN and EN are up, then VCC should come up.

No VCCX should be necessary to start the chip.

Actually, EN should be tied to VIN, not VCC, that is an issue, remove R36 and R37.

Please try this and see if behavior improves.

-Orlando

Orlando,

Thanks for your advices!

Does the internal VCC regulator have over-current protection? Is there a limit of max. capacitance allowed on the VCC line?

On my board, the VCC is 0V when it's not starting. However, with a jump-start on VCCX, the internal VCC regulator keeps working even when the output is shutdown for some unknow reasons. The internal VCC regulator seems working fine in this case.

I will try tyeing the ENs to VIN. However, what are the reasons behand it? Per the data sheet, as long as the ENs get to above 2V, the channels should start to work. Do EN pins provide extra helps for the starting up?

The issues that I am straggling with are:

Thanks a lot.

Kang

Kang,

EN voltage turns on VCC, that's why EN needs to be referenced to VIN and not VCC, otherwise it will not turn itself on.

When you use VCCX that will pull up VCC, which then pulls up EN, that's the "jump-start" mechanism you're referring to.

The longer HS FET on-time might be associated with diode emulation mode. Are you able to configure FPWM?

-Orlando

Orlando,

Connecting EN directly to VIN resolves the start-up issue. Thanks a lot!

Unfortunately, I am not able to configure FPWM -- there is a trace directly connect DEMB pin to GND beneath the chip. Would the diode emulation mode cause the chip jumps to the minimum duty cycle when increasing the input voltage to around 40V?

I have tried a few different crossover frequencies with sufficient phase margin. But that does not help at all. Each case, the output voltage collapses at about the same input voltage - 40V.

Would you suggest what else I could try?

Thank you.

Kang

Kang,

I don't expect output voltage to fall with higher input voltage, there is no overvoltage option.

Is VCC voltage up when this happens? Does the gate driver output?

What do the waveforms look like when this happens?

Let me know,

-Orlando

Orlando,

When the output collapsed, the VCC is 5V and stable. The gate driver is pulsing at the minimum on-time.

The waveforms are attached.

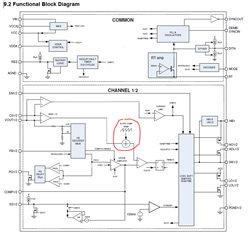

Is there a way the Slope Comp Ramp can be adjusted? (refer to the functional block diagram on page #19 of the data sheet)

Gate_driver_waveform_when_the_output_collapsed.pdf

Gate_driver_waveform_when_the_output_collapsed.pdf

Thank you.

Kang

Kang,

Its unlikely the slope compensation is causing issues, it most likely cannot cause those short on-time pulses.

If the VOUT voltage is low and COMP voltage is high ( >1V ), then the duty cycle should be large.

The only thing I can think of that would cause that short pulse is current limit, maybe at higher VIN theres more noise on SW node and then current limit noise.

Can you add a current sense filter, maybe a capacitor across CS and VOUT pins, right by the IC?

You can maybe try increase your snubbing, right now your resistance is very high 1.2kΩ. Try going down to ~10Ω.

Let me know,

-Orlando

Orlando,

Thanks for your quick responses!

I have tried the filter on the CS line. 100pF/47Ohm. The cap is right at the chip (about 3mm away) between pin 26/27. The filter did not help.

I'll try reducing the snubber resistance.

The waveforms of the rising/falling edges on the SW1 node are attached for your reference. Regular passive probes with ground clip were used to catch the signals. It seems not very noisy.

Thank you so much!

Kang

Hi Kang,

100pF 47ohm set a cutoff frequency of 3MHz, it is a small filter for 300kHz.

Try increasing capacitance to 1nF, that will set a cutoff frequency of 3MHz.

Also did you do the filter for both channels?

-Orlando

Orlando,

Thanks for the input. Actually, I have tried 1nF/47ohm. It did not help.

Since the two-phase operation had the similar problems, to simplify the debugging process, for all the waveforms that I have provided, the EN2 is tied to ground, only CH1 is enabled. Would that have any concerns?

Thanks a lot.

Kang

Kang,

No, the single phase testing is a good idea.

Hmmm can you test with a HO and LO resistor?

5-10Ω should be a good starting point.

It looks like some noise might be coupling onto LO from HO and SW rising.

-Orlando