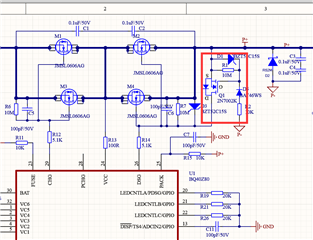

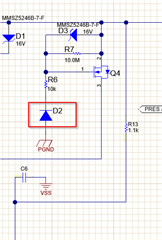

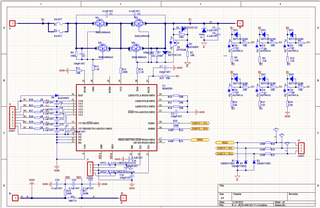

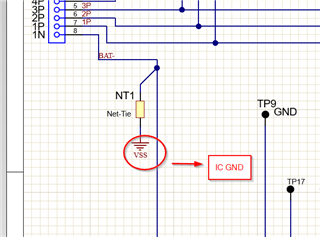

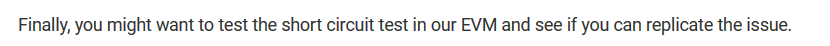

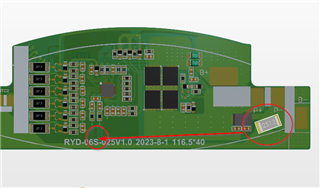

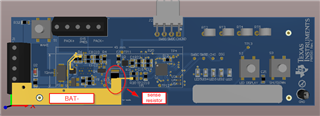

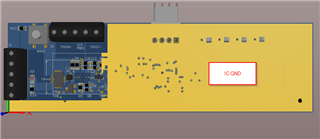

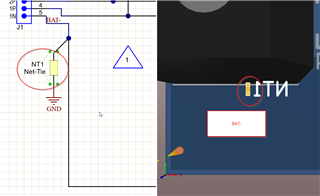

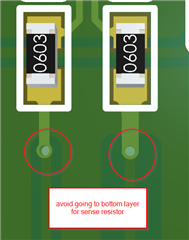

After connecting the anti-reverse circuit shown in the red box in the figure, the test short-circuit protection is not restored, and if the short-circuit protection is still connected to the communication, the communication-related components will be burned out, what is the reason?