Other Parts Discussed in Thread: PMP11254

On normal power supply our circuit of LAN8740 IC heat normal, But on TPS23752 IC POE supply LAN8740 IC heat very much high. Please needful for this.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Pallav,

Thanks for reaching out. Could you share a schematic to let us know how TPS23752 and LAN8740 are connected ? Thanks.

Best regards,

Diang

Hi Diang, any suggestion I have messure current on 12V-P. There is a very much fluctuation in current from 108mA to 280mA approx. Please advise me any suggestions.

Hi Pallav,

Sorry that the PoE team has traveling and multiple works in list recently. Please expect a delay on the E2E reply.

Best regards,

Diang

Hi Pallav,

Thanks for your patience.

Looks like LAN8740A is sourced by 3.3-V. Does the 3.3V comes from 12V-P by a LDO?

Could you measure the 12V-P to see is it stable? If 12V-P is not stable, you can check VC-RTN to see if it is stable.

If either of them are not stable, please help to attach the waveforms you captured. Thanks.

Best regards,

Diang

Hi Diang,

Thanks for reply,

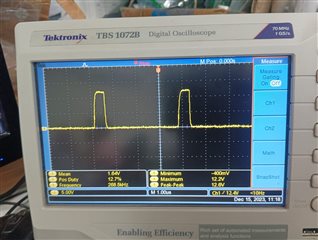

I have measure 54V-POE input, Vc-RTN and 12V-P on DSO. Please check and give suggestion.

1. 54V-POE

2. Vc-RTN

3. 12V-P

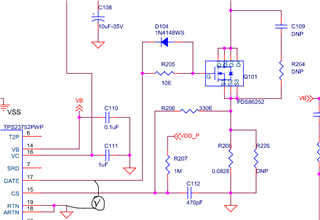

I need more question about schematic.

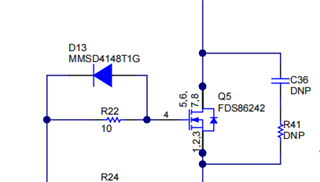

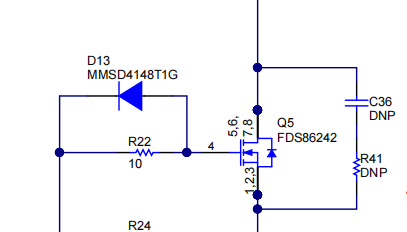

We make our design, as per PMP11254 referance design. What is a role of below D13 diode in Gate drive.

Our device is Air tight so heating of POE section, PCB is heating very much high.

Please help me regarding above issue.

Looking forward to hearing you!

Best Regards,

Pallav

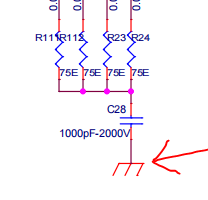

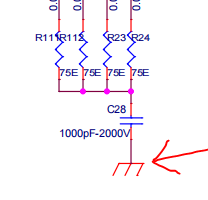

Also give me one suggestion for below circuit.

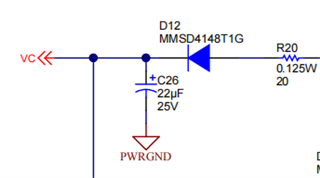

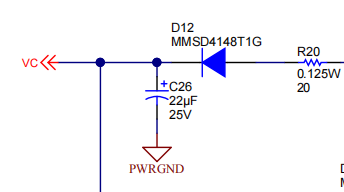

What is happen when swap D12 and R20 position in circuit. Because in datasheet diode and resistor position swap in typical circuit.

I have do in my board on Monday. board working fine till now.

Please give us your suggestion for below circuit.

Please give me above two comment answer.

Looking forward to hearing you!

Best Regards,

Pallav

Hi Pallav,

Thanks for your information.

1. D13 ensure a fast switching off speed for Q5. This can help to reduce the switching off energy. If you have a secondary side sync FET, this also help to reduce the pri-sec FETs shoot-though time.

2.There should be no issue to swap D12 and R20 position.

3. The 12V-P voltage has 1.68-V peak-peak ripples. Just wondering if you have a LDO to transformer 12V-P to to 3.3-V input to source LAN8740A. Normally LDO should alleviate most of the ripples.

4. For the output ripple, looks VC is higher than the UVLO and VDD is stable too. Could you help measure the GATE-RTN voltage? Just wondering if the GATE is discontinuous that causes large ripples on 12V-P.

Best regards,

Diang

Hi Diang,

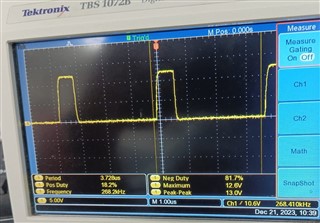

Please find waveform of GATE-RTN Voltage as below,

One other query,

Please find attachment file.

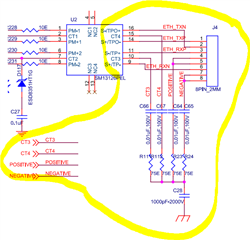

If i connect Center tap and TX RX pin as per pdf.

Is there any problem occurs in future?

if yes please kindly send me detail of that problem.

Best Regards,

Patidar Pallav

Hi Pallav,

Thanks for your updates.

Sorry I have ran out of time recently. I will get back to you by next Wednesday.

Best regards,

Diang

Hi Pallav,

Thanks for the gate voltage waveforms. The duty cycle (D) is about 17%. And the turns ratio is 2:1.

By N*Vout = D/(1-D) * Vin, Vin is ~117V, which is higher than the 54V-POE input. Looks like the gate duty cycle could be varying at the same load current or the load is too light. Could you help to check:

- a zoom-out gate waveforms to see if the duty cycle is keeping at ~17% or it is variable at the same load current

- if the Vout could be stable when you have a heavier load.

Best regards,

Diang

Hi Diang,

I have attached photo for Gate waveform when load as only our device, vary duty cycle 12% - 16%

I have attached photo for Gate waveform when load as only our device + Lock, vary duty cycle 17% - 18%.

In Some devices get back from field, which has issue regarding Vc pin damage (It show continuity, or it show low impedance).

We check waveform in which we find ripples approx. 1.2V peak to peak, right now we reduce peak to peak voltage up to 440mV to 600mV with added 4.7uF-50V capacitor at Vc pin.

Also, we reduce output voltage 12V-P ripples up to 280mV with added 47uF-50V Ceramic capacitor.

What more protection we need to take care for this issue. will it help when we added 12V Zener at Vc pin?

Hi Pallav,

Thanks for your updates.

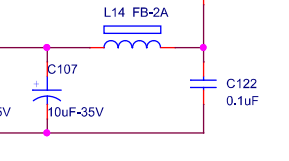

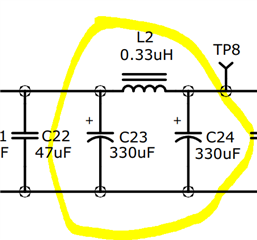

I saw you add a CLC pi-filter before Vout, and I am wondering if you could increase the inductor inductance meanwhile keep it not saturated. It may further helps to reduce the Vout ripple.

Best regards,

Diang

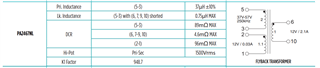

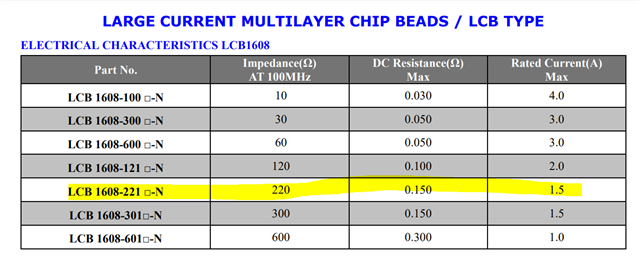

We are using LCB1608-221Y-N for L14. Please find attachment datasheet. Let me know, Is it ok or not?

Hi Pallav,

LCB1608-221Y-N is rated for 1.5A. I am wondering what is your output power at 12-V. Looks like P needs to be smaller than 18W.

Using 2*pi*100e6*L=220, L is ~0.35 uH at 100MHz. You can try to further increase the inductance to 2.2 - 4.7 uH which may help to flat the current and the voltage ripples.

Best regards,

Diang

We decide to change this L14 Value to BLM18SG121TN1D for increase the power capability at 12V. Is it suitable for our device?

Hi Pallav,

With the holidays here, many device experts are currently out of the office. When they return they will look into this and provide a response. Please expect some delay accordingly.

Thanks,

Field

Hi Diang,

Hope you are doing well.

In our design we use plastic Cat5 Jack for POE connections. Is it correct circuit, which is I have sent earlier (we connect Earth ground, but we use plastic Cat5 Jack), or we need to change GND at Bob-Smith terminations?

Best Regards,

Pallav Patidar

Hi Pallav,

Happy new year!

For the inductance value in PI-filter, normally a large inductance of the inductor and a small stray inductance in the capacitors can make the performance better. BLM18SG121TN1D is a 0603 packaged one and it may not be large enough. You can use the following link to help design a filer: www.ti.com/.../SSZT824

The J4's terminal to rectifier looks good to me.

Best regards,

Diang

Hi Diang,

Please give us an answer of this comment.

In our design we use plastic Cat5 Jack for POE connections. Is it correct circuit, which is I have sent earlier (we connect Earth ground, but we use plastic Cat5 Jack), or we need to change GND at Bob-Smith terminations?

Best Regards,

Pallav Patidar

Hi Pallav,

The J4's terminal to rectifier looks good to me from the schematic. Did you also connect Cat5 Jack to earth or chassis?

Best regards,

Diang

Hi Diang,

J4 is plastic connector so there is a not any earth or chassis ground. So, where we connect below Gound? shall we connect that with common ground?

Best Regards,

Pallav Patidar

Hi Pallav,

The Bob-Smith termination ground normally depends on the product application.

For products are in plastic RJ45, some of the BS plane ground is left floating or connecting to output ground.

Best regards,

Diang

Hi Diang,

Right now, In our layout our earth ground is connected with floating plane. Is it correct or wrong? OR Is it problem for heating?

Best Regards,

Pallav Patidar

Hi Pallav,

We did see some products make the Bob-Smith termination ground floating when a plastic RJ45 is used. It may depend on the product application, and looks like floating is optional.

This is more related to EMI and I do not think it has big impact for heating.

Best regards,

Diang

Hi Pallav,

I will close this thread for now. Please reply or open a new thread if you have further questions.

Best regards,

Diang