Hello,

I have a problem with TPS27S100 partnumber.

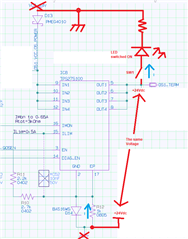

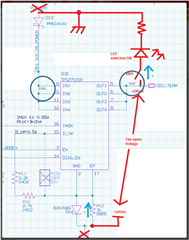

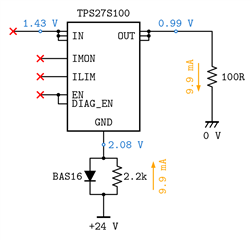

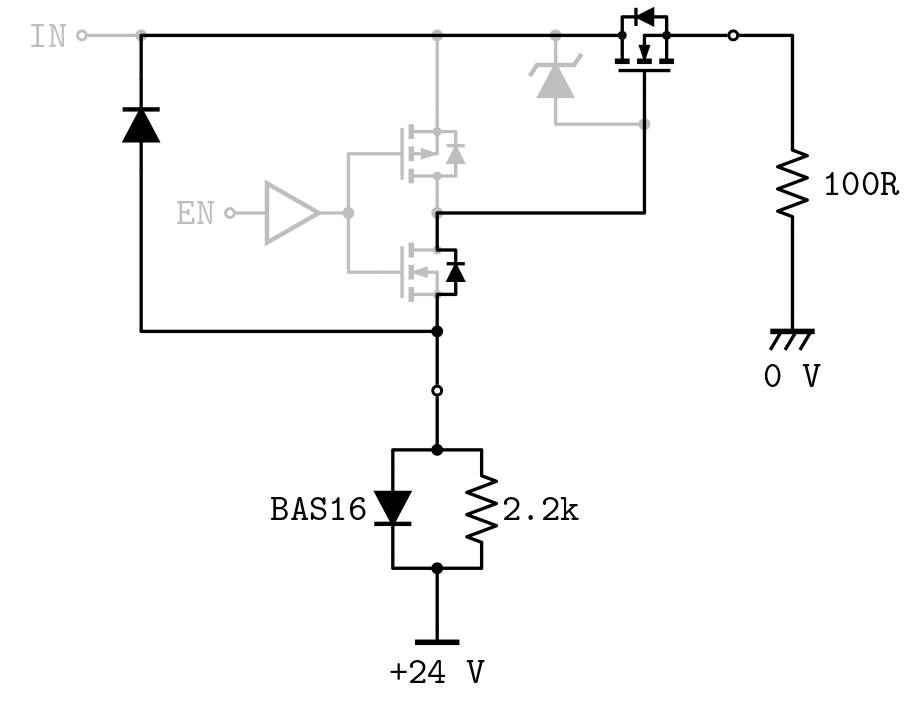

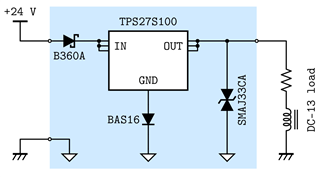

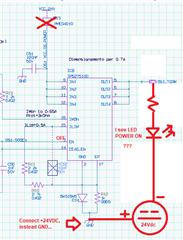

I report the test in this schematics:

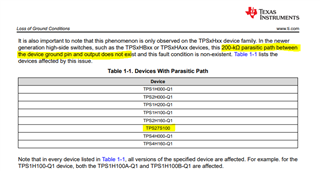

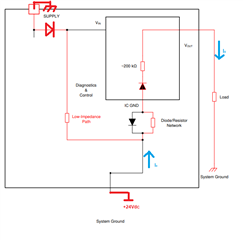

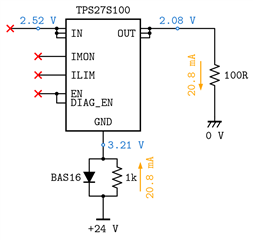

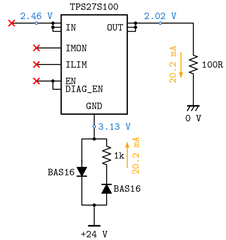

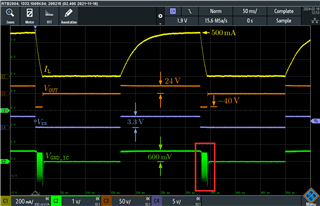

When I connect only +24Vdc to GND Network, the output go HIGH and i see led power on.

This always happens even if I don't activate the EN pin (pin 3).

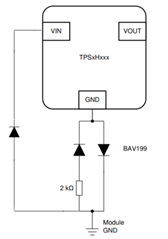

If i remove R12 the output is LOW, but in this case i loose the reverse current protection in case of inductive load.

Can you help me?

Many thanks.

Best regard.