Dear support,

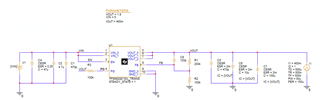

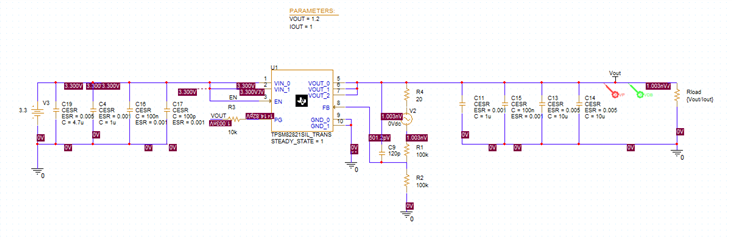

As mentionned in the related question "TPSM82821: max output capacitance" I also have some more capacitance (>66µF) away from the converter behind a ferrite bead. I try to do some simulations on Pspice to see wether it affects stability but I can not manage to get relevant results.

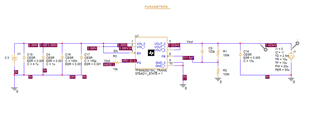

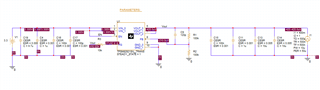

Here is the circuit I try to simulate (at first simple, without addind the extra capcitance and the ferrite):

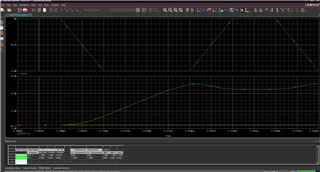

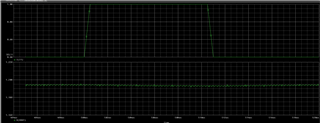

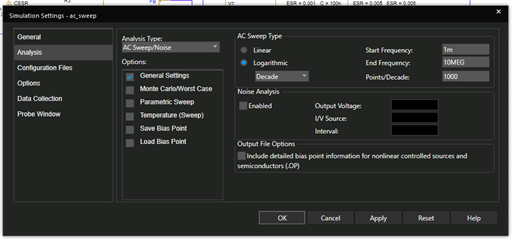

My simulation profile is the following:

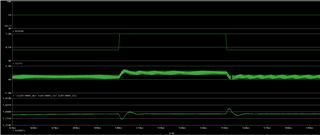

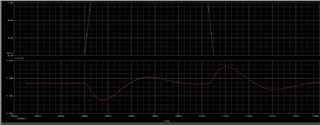

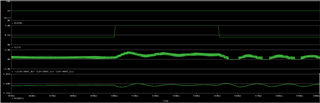

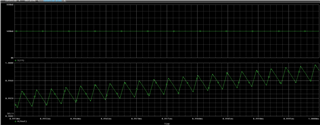

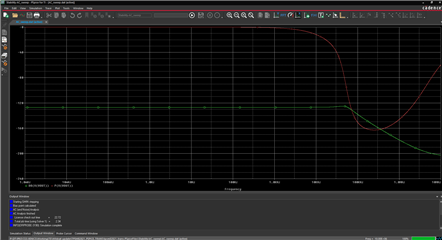

And here are the curves I get:

The curves seem to be completely wrong. It is not even possible to compute the phase margin (phase shift when the magnitude plot crosses 0dB). What am I doing wrong?

Thank you in advance for your help,