Other Parts Discussed in Thread: TPS25980, TPS2597

Hi TI experts,

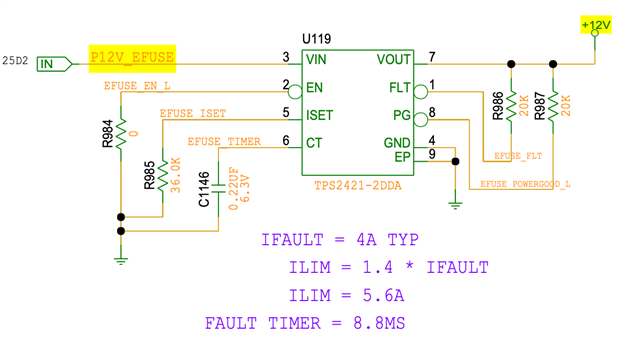

In my design, i have put TPS2421-2 as current limiter after a flyback converter. Below is the schematic.

P12V_EFUSE comes from flyback output. +12V will be provided to downstream DC-DC converters.

As EN is held low, that means +12V starts ramping once P12V_EFUSE crosses the UVLO.

Does below design work? Is there any risk that both input and output are rising simulataneously?