HI there,

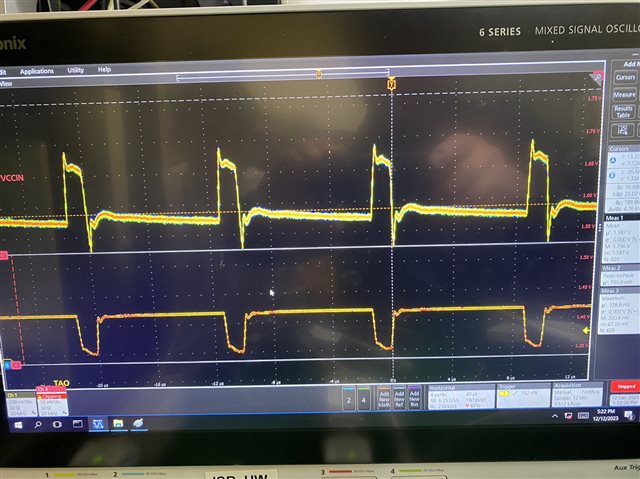

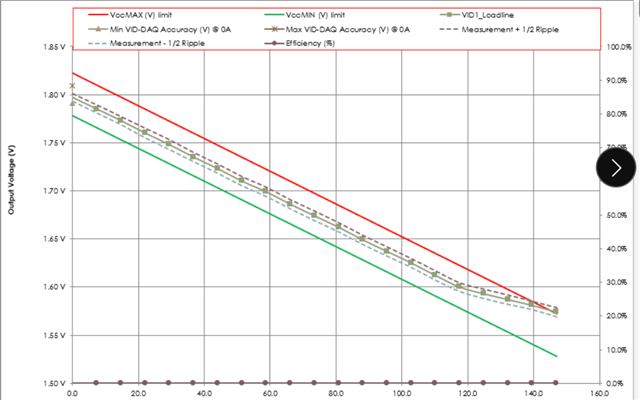

We tested failure on TPS53688 VRTT Transient_LL test #1. The measured Vdrop is quite low.

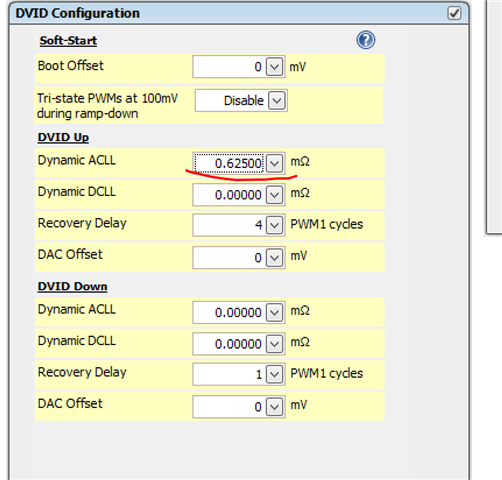

During debug, found reducing AC Loadline helps, but TI confirmed there is a known issue that AC LL should be set close matching DC LL.

With reduced AC loadline, we got failure on STATIC_LL test cases.

How can this be fixed?

Please advise anything else we can try to pass Transient_LL.

Thanks.