Hi All,

We are having an issue where the SCD protection appears to be causing the DSG FETs to fail short. Schematics attached for reference.

The circuitry attached to TS2 is not fitted, please ignore.

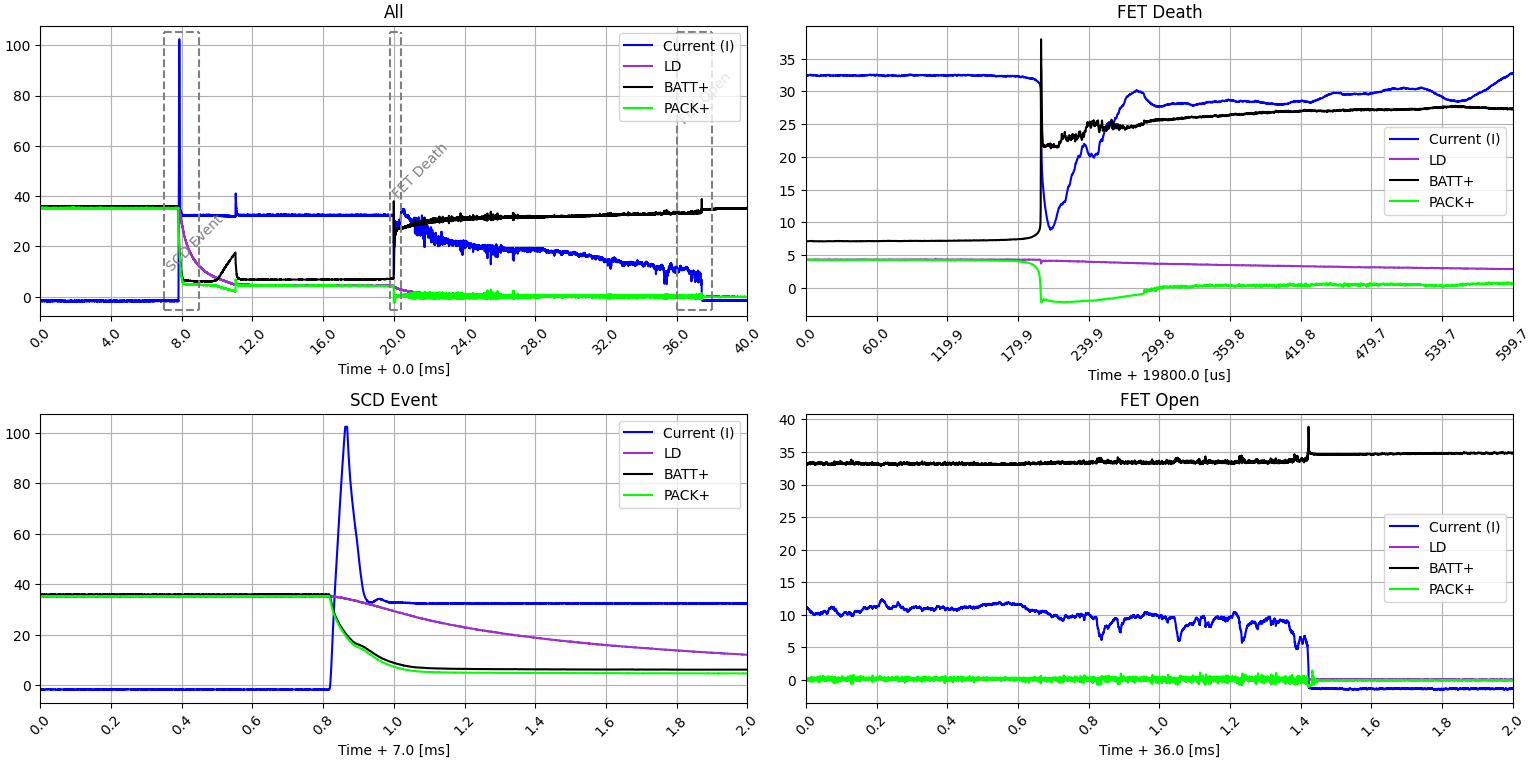

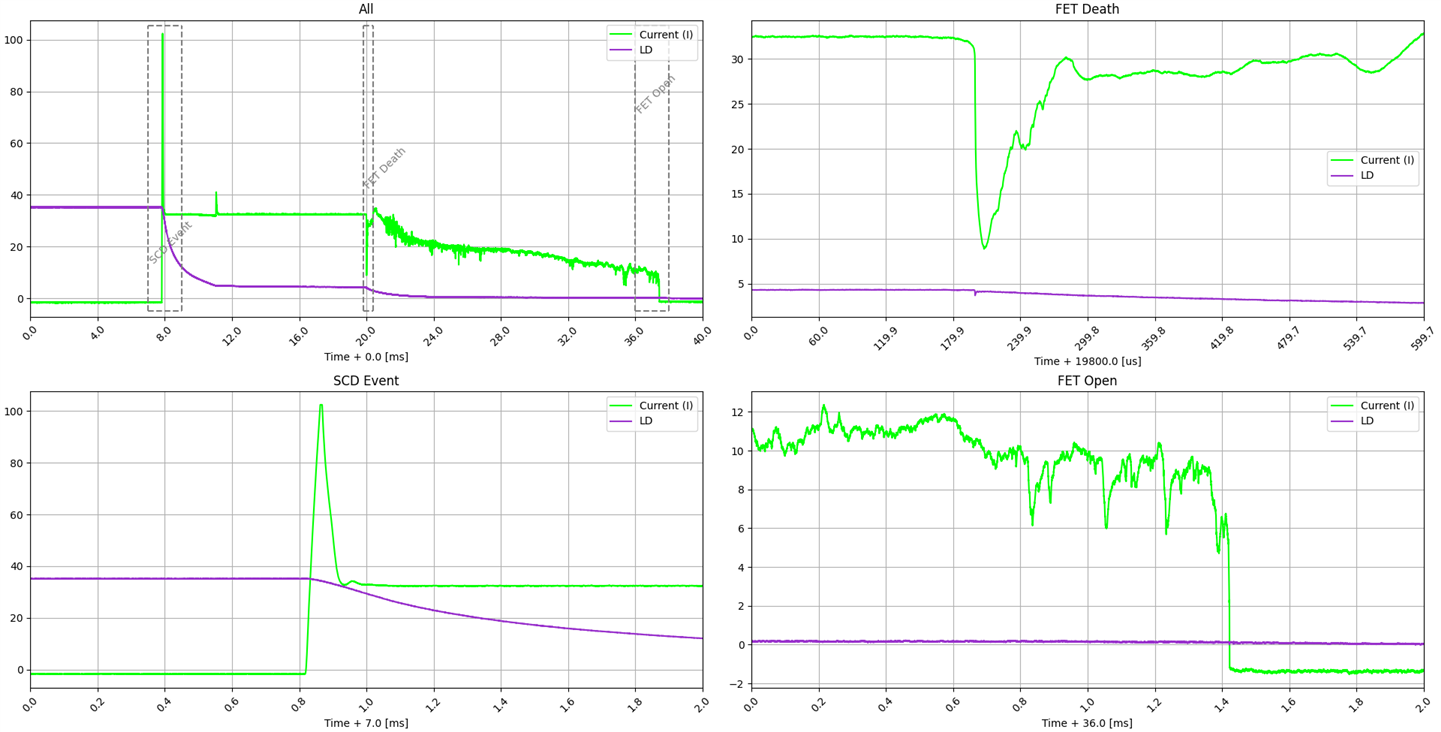

The plots attached below show a lot of what we believe is going on:

If we look at the top left plot first:

- There the black spike shows the discharge current under short circuit conditions

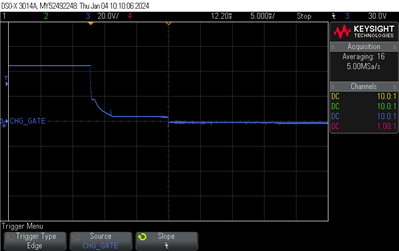

- The Gate drive voltage (RED) is nice and clear of the source voltage (BLUE) value and appears to begin clamping towards 0V to turn off the FETs. Part way through this clamp, something happens where this process stops, the values seem to get stuck and we assume at this point the FETs are blowing.

These details can be seen in more detail in our zoomed in plots titled as marked on the Full plot.

In 'SCD event' plot we can see that the gate voltage drops sharply as the protection kicks in but fails to clamp completely.

This is a 10S1P Battery pack using Molicel P42A (Cell Stack typical DC impedance ~160mOhm) and SIR180DP MOSFETs with the BQ79652.

25V Min 42V Max 36V Nom

Any help to solve this problem is appreciated, I can also collect any more data required.

Thanks

Ben