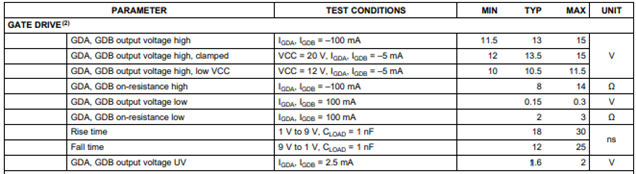

Hi,

We are using UCC28061 as a controller in our interleaved PFC design. We are dealing with the MOSFET failure after turning off/on the board. After turning off, we detected that the MOSFET in PFC circuit goes to short circuit in the case of cut-off. As can be seen in the scope view, at the turn off condition, the transient drain current is10A and after the gate voltage turns to cut-off situation, ringing occurs at the MOSFET gate terminal. As recommended in the datasheet, to eliminate damp ringing, we also put a small series resistance (10R) to gate drive, but the ringing continues to show up which causes short circuit of MOSFET as can be seen in below.

We detected that gate is drived involuntarily that forces to turned on the MOSFET (Not in linear region)

What could be the cause of this behavior?

Do you have any solution for this unexpected behavior?

Yellow: Drain Voltage (100V/div)

Blue: Drain current (5V/div)

Green: MOSFET Gate voltage (20V/div)

Time div:40ns